# INSTITUTO TECNOLÓGICO DE CIUDAD MADERO DIVISIÓN DE ESTUDIOS DE POSGRADO E INVESTIGACIÓN MAESTRIA EN INGENIERÍA ELÉCTRICA

#### **TESIS**

# DISEÑO E IMPLEMENTACIÓN DE UN INVERSOR MMC CON ALGORITMO DE CONTROL DE VOLTAJES EN LOS CAPACITORES

Que para obtener el Grado de Maestro en Ingeniería Eléctrica

Presenta Ing. Alfredo Yojanam Alejandre López G10070123

Directora de Tesis

Dr. Pedro Martín García Vite

Instituto Tecnológico de Ciudad Madero

Cd. Madero, Tams., a 05 de Diciembre de 2018

OFICIO No.: U2.136/18

ÁREA: DIVISIÓN DE ESTUDIOS DE POSGRADO E INVESTIGACIÓN

**ASUNTO:** AUTORIZACIÓN DE IMPRESIÓN

DE TESIS.

ING. ALFREDO YOJANAM ALEJANDRE LÓPEZ NO. DE CONTROL G10070123 PRESENTE

Me es grato comunicarle que después de la revisión realizada por el Jurado designado para su examen de grado de Maestría en Ingeniería Eléctrica, el cual está integrado por los siguientes catedráticos:

PRESIDENTE:

DR.

PEDRO MARTÍN GARCÍA VITE

**SECRETARIO:**

DR.

GASTÓN HERNÁNDEZ MARTÍNEZ

VOCAL:

M.C.

RAFAEL CASTILLO GUTIÉRREZ

SUPLENTE:

M.C.

HERMENEGILDO CISNEROS VILLEGAS

**DIRECTOR DE TESIS:**

DR.

PEDRO MARTÍN GARCÍA VITE

Se acordó autorizar la impresión de su tesis titulada:

"DISEÑO E IMPLEMENTACIÓN DE UN INVERSOR MMC CON ALGORITMO DE CONTROL DE VOLTAJES EN LOS CAPACITORES"

Es muy satisfactorio para esta División compartir con Usted el logro de esta meta, esperando que continúe con éxito su desarrollo profesional y dedique su experiencia e inteligencia en beneficio de México.

ATENTAMENTE

the

Excelencia en Educación Tecnológica "Por mi patra y por mi bien"

DR. JOSÉ AARÓN MELO BANDA JEFE DE LA DIVISIÓN DE ESTUDIOS DE POSGRADO E INVESTIGACIÓN and the second

SECRETARÍA DE EDUCACIÓN PÚBLICA

TECNOLÓGICO NACIONAL

DE MÉXICO

INSTITUTO TECNOLÓGICO DE CUDAD MADERO

DIVISIÓN DE ESTUDIOS DE POSGRADO

E INVESTIGACIÓN

c.c.p.- Archivo Minuta

JAMB 'RCG 'mdcoa\*

# **Dedicatoria**

La presente tesis la dedico a toda mi familia y amigos, principalmente a mi madre Maria Elena López lugo, que ha sido un pilar fundamental en mi formación como profesional, por brindarme la confianza, consejos, oportunidad y recursos para lograrlo, a mi padre Alfredo Alejandre Antonio, gracias por brindarme apoyo para poder realizar mi formación profesional.

# Agradecimientos

Agradezco a dios padre por haberme brindado salud y dejarme vivir este logro tan importante para mi vida. Agradezco a mi familia por haberme dado este apoyo necesario para realizar mi formación profesional. También al Instituto Tecnológico de Cd. Madero (I.T.C.M), por haber sido mi casa de estudios, así como todos los maestros de esta institución por brindarme una buena formación profesional, así como también la División de Estudios de Posgrado e Investigación del (I.T.C.M), por haberme otorgado la oportunidad de realizar mis estudios de maestría.

Diseño e implementación de un inversor MMC con algoritmo de control de voltajes en los

capacitores

Resumen

Presenta: Alfredo Yojanam Alejandre López

Asesor: Dr. Pedro M. García Vite

En el presente trabajo en el cual se diseñó un inversor multinivel de cd-ca implementando

un algoritmo de balanceo en los voltajes de los capacitores y en este convertidor se realizó el es-

tudio necesario para poder saber el número de submódulos (SMs) que se requieren para generar

7 niveles en la salida, se simularon todas sus partes, en dicha simulación fue implementado un

inversor monofásico y otro trifásico junto con el algoritmo de balanceo de voltaje.

Al abordar el tema de los Convertidores Multinivel, se habla de cada componente; sub-

módulos o celdas de módulos bidireccional conectadas en cascada con un conductor buffer en

cada pierna o fase. Para llevar a cabo la tarea de conversion los inversores tradicionales de 2

niveles son ampliamente utilizados pero presentan desventajas como pérdidas de conmutación

y la necesidad de grandes filtros. Para enmendar estos problemas se desarrollaron tecnologías

multinivel como el inversor de diodo anclado, el inversor de capacitor flotante y el inversor de

fuentes independientes en cascada, la característica de este último, es la capacidad de alto voltaje

con dispositivos de voltaje limitado, baja distorsión armónica, menor pérdida de conmutación,

eficiencia alta, buena compatibilidad electromagnética, facilidad de distribución y encapsulado

para optimizar el circuito ya que cada nivel de voltaje tiene la misma estructura.

Ш

Considerando que los MMC, se pueden modular a frecuencias de línea de 60 Hz, los voltajes de los capacitores de cada submódulo se pueden ver desbalanceados, lo cual provoca una desestabilidad del inversor, la cual es necesaria una estrategia de control que combine una técnica de modulación, permitiendo el balanceo y el control de cada voltaje, con el fin de sintetizar un voltaje controlado en la salida del inversor multinivel, se propone un algoritmo que ordene y balancé los voltajes de cada capacitor. Dicho algoritmo de control basado en un ordenamiento por comparación se puede tener un control local para cada subrama en el MMC, así la tarea de regulación se ataca localmente, de esta forma siendo controlada por un microcontrolador maestro.

Los convertidores de c.d. a c.a. se consideran como inversores su objetivo principal es modificar un voltaje de entrada de c.d. a un voltaje simétrico de salida c.a. con una magnitud y frecuencia deseada. El voltaje como la frecuencia puede ser fija o variable. En la actualidad los inversores multinivel se consideran como los convertidores de potencia con mayor demanda en la industria, por ser los más adecuados para aplicaciones donde se requiera media tensión y alta potencia. Existen diversos algoritmos de balanceo para regular el voltaje en los capacitores, cuya función principal es ordenar los voltajes en cada capacitor y elegir quien se carga o se va a descargar. Según la dirección de la corriente del brazo.

Las siguientes simulaciones de un MMC monofásico se emplea el algoritmo, al igual de un diagrama hecho en Simulink que usa 6 SMs, para cada brazo, esos SMs están dentro de un bloque, dentro de los cuales se ven más bloques de señales en el Simulink y su estructura lo componen de 4 bloques, los bloques de señal como : el bloque que genera las señales triangulares, el bloque señal PWM, mientras otro bloque se encarga de medir el voltaje de cada SM y la corriente total de cada brazo y por último se manda al bloque del algoritmo propuesto del proyecto. La señal de voltaje triangular entra a un bus para ser enviada después al bloque PWM. La modulación de ancho de pulso es la comparación de una señal triangular o señal portadora contra una señal senoidal o referencia. Avanzando al capítulo 4 se describen los resultados del inversor, utilizando la teoría explicada en el capítulo 2, el fin de decidir la cantidad de SMs con el fin de generar una onda escalonada de 7 niveles parecida a una onda senoidal, se muestran las valida-

ciones experimentales con un SM, 4 SMs y 6 SMs, el uso de 2 microcontroladores ATmega 328p para generar las señales de control de los transistores. Recordando que dependiendo de que nivel se necesite se realiza el estudio para obtener el número de SM requeridos para el nivel deseado.

*Palabras claves*— convertidor modular multinivel (MMC), Modulación Vector espacial (SVM), Modulación de ancho de pulso (PWM), Submódulo (SM).

Design and implementation of an MMC inverter with voltage control algorithm in the

capacitors

**Abstract**

Presents: Alfredo Yojanam Alejandre López

Advisor: Dr. Pedro M. García Vite

In the present work in which a multi-level inverter of cd-ca was designed implementing a

balancing algorithm in the voltages of the capacitors and in this converter the necessary study

was carried out to be able to know the number of SMs that are required to generate 7 levels in

the output, all its parts were simulated, in this simulation a single-phase and three-phase inverter

was implemented together with the voltage balancing algorithm.

When addressing the issue of Multilevel Converters, each component is discussed; submo-

dules or bidirectional module cells connected in cascade with a buffer conductor in each leg

or phase. In order to carry out the conversion task, the traditional 2-level inverters are widely

used but have disadvantages such as switching losses and the need for large filters. To correct

these problems, multilevel technologies were developed, such as the clamped diode inverter,

the floating capacitor inverter and the inverter from independent sources in cascade. The latter's

characteristic is the high voltage capacity with limited voltage devices. low harmonic distortion,

lower switching loss, high efficiency, good electromagnetic compatibility, ease of distribution

and encapsulation to optimize the circuit since each voltage level has the same structure.

Considering that MMCs can be modulated at 60 Hz frequencies, the voltages of the capa-

citors of each submodule can be seen unbalanced, which causes an inverter's instability, which

VI

is necessary a strategy of control that combines a modulation technique, allowing the balancing and control of each voltage, in order to synthesize a controlled voltage at the output of the multilevel inverter, an algorithm is proposed to order and balance the voltages of each capacitor. Suchas control algorithm based on a sorting by comparison can have a local control for each sub-branch in the MMC, so the regulation task is attacked locally, in this way being controlled by a master microcontroller.

The converters of c.d. a.c. The inverter's main objective is to modify an input voltage of c.d. at a simulated output voltage c.a. with a desired magnitude and frequency. The voltage as the frequency can be fixed or variable. Currently multilevel inverters are considered as the power converters with the highest demand in the industry, as they are the most suitable for applications where medium voltage and high power are required. There are several balancing algorithms to regulate the voltage in the capacitors, whose main function is to order the voltages in each capacitor and choose who is charging or going to download. According to the direction of the arm current.

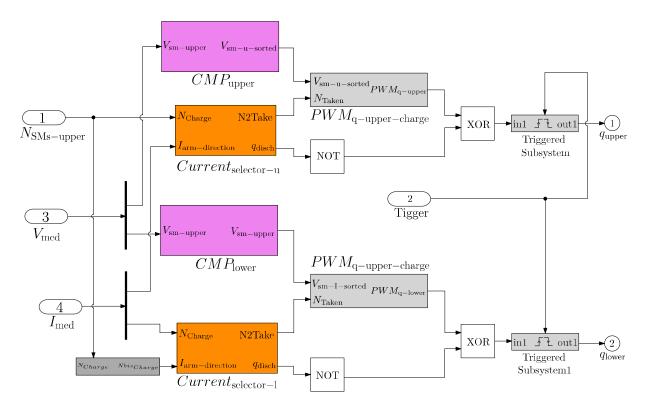

n the proposed algorithm, it first contemplates the ordering of the sMs voltage, according to the voltage level present in them. The following simulations of a single-phase MMC algorithm is used, as well as a diagram made in Simulink that uses 6 SMs, for each arm, those SMs are inside a block, within which more blocks of signals are seen in the Simulink and its structure consists of 4 blocks, the signal blocks such as: the block that generates the triangular signals, the PWM signal block, while another block is responsible for measuring the voltage of each SM and the total current of each arm and finally it is sent to the block of the proposed algorithm of the project. In the internal module of the algorithm the following blocks are observed:  $CMP_{upper}$  and  $CMP_{lower}$ , inside is part of the algorithm whose function is to order the voltage of the capacitors, another existing block is the one of synchronization is a logic gate XOR, responsible for choosing who is inserted and who does the opposite and finally is a block of registration. Advancing to chapter 4 the results of the investor are described, using the theory explained in chapter 2, in order to decide the amount of SMs in order to generate a stepped wave of 7 levels similar to a sine wave, the experimental validations are shown with a SM, 4 SMs and 6 SMs,

the use of 2 ATmega 328p microcontrollers to generate the control signals of the transistors. Remembering that depending on what level is needed the study is done to obtain the number of SM required for the desired level.

*Keywords*– Modular Multilevel converter (MMC), Pulse width modulation (PWM), Space vector modulation (SVM), Submódulo (SM).

# Índice general

| 1 | Intr | oducción                                              | 1  |

|---|------|-------------------------------------------------------|----|

|   | 1.1  | Antecedentes                                          | 3  |

|   | 1.2  | Planteamiento del problema                            | 4  |

|   | 1.3  | Propuesta de solución                                 | 4  |

|   | 1.4  | Justificación                                         | 4  |

|   | 1.5  | Objetivo general                                      | 5  |

|   |      | 1.5.1 Objetivos específicos                           | 5  |

|   | 1.6  | Hipótesis                                             | 5  |

|   | 1.7  | Alcances y limitaciones                               | 5  |

|   |      | 1.7.1 Alcance                                         | 5  |

|   |      | 1.7.2 Limitaciones                                    | 6  |

|   | 1.8  | Conclusión                                            | 7  |

| 2 | Mar  | co teórico                                            | 8  |

|   | 2.1  | Descripción del inversor                              | 9  |

|   | 2.2  | Clasificación de los inversores                       | 9  |

|   | 2.3  | Descripción del Inversor multinivel                   | 11 |

|   |      | 2.3.1 Topología del MMC                               | 11 |

|   | 2.4  | Análisis de un SM con configuración HB                | 13 |

|   | 2.5  | Tipos de modulación para multinivel                   | 18 |

|   | 2.6  | Modulación por vector espacial                        | 19 |

|   |      | 2.6.1 Fórmulas para calcular los niveles del inversor | 20 |

|   | 2.7  | Algoritmos de ordenamiento                            | 22 |

|   | 2.8  | Inversor monofásico y trifásico de multinivel         | 23 |

|   | 2.9  | Conclu  | asiones                                                          | 25 |

|---|------|---------|------------------------------------------------------------------|----|

| 3 | Algo | oritmos | para el control de voltaje de los capacitores                    | 26 |

|   | 3.1  | Algori  | tmos existentes                                                  | 27 |

|   | 3.2  | Algori  | tmo propuesto                                                    | 28 |

|   | 3.3  | Simula  | ación del algoritmo propuesto                                    | 31 |

|   |      | 3.3.1   | Simulación de una fase o pierna                                  | 31 |

|   |      | 3.3.2   | Simulación de un brazo                                           | 33 |

|   |      | 3.3.3   | Bloque del SM en Simulink                                        | 33 |

|   |      | 3.3.4   | Bloques de señales en el Simulink                                | 34 |

|   |      | 3.3.5   | Señal de voltaje triangular                                      | 35 |

|   |      | 3.3.6   | Modulación de ancho de pulso (PWM)                               | 37 |

|   |      | 3.3.7   | Bloque Measurements                                              | 38 |

|   |      | 3.3.8   | Módulo interno del algoritmo                                     | 39 |

|   |      | 3.3.9   | Algoritmo Propuesto bloque de Ordenamiento                       | 40 |

|   |      | 3.3.10  | Medición de la corriente                                         | 42 |

|   |      | 3.3.11  | Voltaje de los capacitores balanceados en el brazo superior      | 42 |

|   | 3.4  | XOR y   | sincronización                                                   | 43 |

|   | 3.5  | Simula  | ación trifásica del algoritmo de regulación de voltaje en un MMC | 45 |

|   | 3.6  | Regula  | ación de los voltajes de cada capacitor                          | 46 |

|   | 3.7  | Conclu  | asiones                                                          | 48 |

| 4 | Desa | arrollo |                                                                  | 49 |

|   | 4.1  | Valida  | ción experimental de un submódulo (SM)                           | 50 |

|   | 4.2  | Valida  | ción experimental con 4 SMs                                      | 54 |

|   | 4.3  | Valida  | ción experimental con 6 SM                                       | 61 |

|   | 4.4  | Conclu  | asiones                                                          | 70 |

| 5 | Resi | ıltados | y Conclusiones                                                   | 71 |

|   | 5.1  | Result  | ados de un SM                                                    | 72 |

|   | 5.2  | Result  | ados con 4 SMs                                                   | 73 |

| Bi | ibliog | rafía                | 78 |

|----|--------|----------------------|----|

|    | 5.5    | Trabajos Futuros     | 77 |

|    | 5.4    | Conclusiones         | 75 |

|    | 5.3    | Resultados con 6 SMs | 74 |

# Índice de tablas

| Tabla 2.1  | Variables empleadas en el MMC                                          | 12         |

|------------|------------------------------------------------------------------------|------------|

| Tabla 2.2  | Estados de conmutación de un SMs para $(i_o < 0)$                      | 15         |

| Tabla 2.3  | Estados de conmutación de un SMs para $(i_o > 0)$                      | 16         |

| Tabla 2.4  | Estados de conmutación, dirección de la corriente y el estado de carga |            |

|            | del capacitor para $(i_o > 0)$                                         | 17         |

| Tabla 2.5  | Estados de conmutación, dirección de la corriente y el estado de carga |            |

|            | del capacitor para $(i_o < 0)$                                         | 17         |

| Tabla 3.1  | Tabla de los valores de $V_{ m tri}$                                   | 36         |

| Tabla 3.2  | Tabla de la verdad de la compuerta XOR                                 | 44         |

| T 11 41    |                                                                        | <b>7</b> 1 |

| Tabla 4.1  | Estados de conmutación para $S_1, S_2 \dots \dots \dots \dots \dots$   | 51         |

| Tabla 4.2  | Estados de conmutación                                                 | 55         |

| Tabla 4.3  | Estados de conmutación                                                 | 62         |

| Índice     | de figuras                                                             |            |

| Figura 2.1 | Clasificación de los inversores                                        | 10         |

| Figura 2.2 | Diagrama de un MMC con una carga trifásica RL                          | 12         |

| Figura 2.3 | Estados básicos de conmutación de un SM con $(i_o < 0)$                | 14         |

| Figura 2.4 | Estados básicos de conmutación de un SM con $(i_o > 0)$                | 15         |

|            |                                                                        |            |

| Figura 2.5  | Diagrama de los ocho vectores obtenidos a partir de la transformación $\alpha$ |    |

|-------------|--------------------------------------------------------------------------------|----|

|             | y $\beta$                                                                      | 20 |

| Figura 2.6  | Circuito equivalente para el análisis de los voltajes de fase                  | 21 |

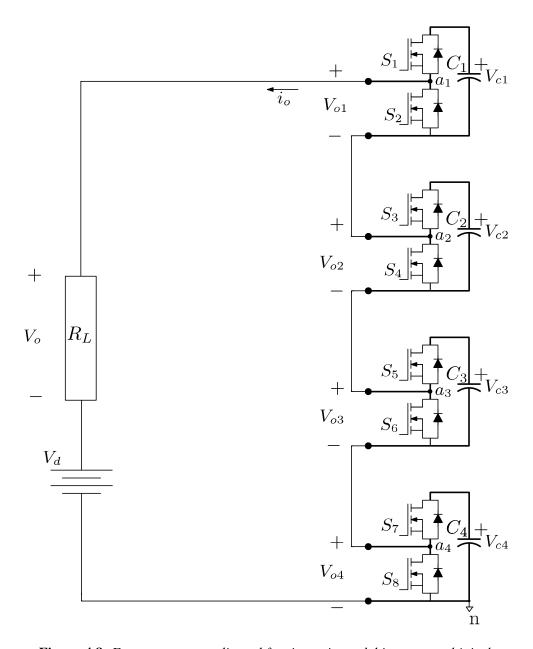

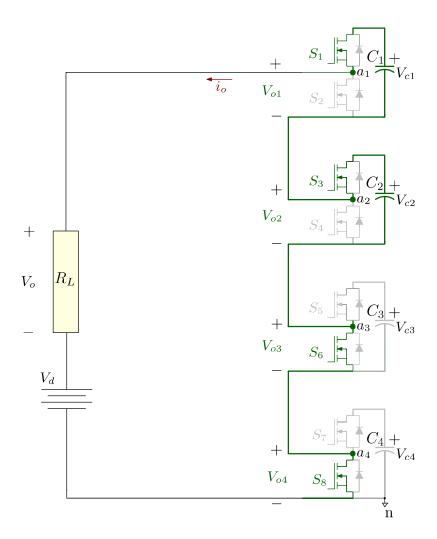

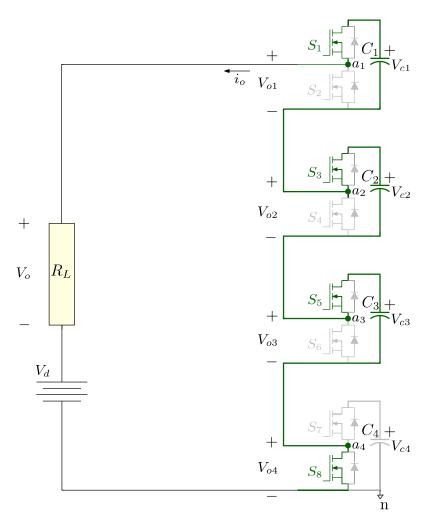

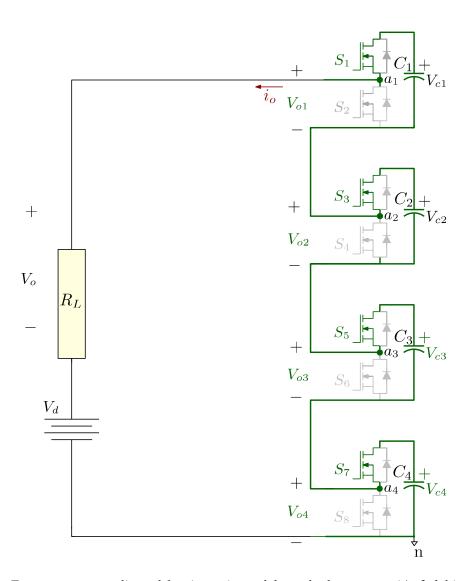

| Figura 2.7  | Inversor Multinivel Monofásico                                                 | 23 |

| Figura 2.8  | Inversor Multinivel Trifásico                                                  | 24 |

| Figura 3.1  | Diagrama de bloques del comparador de niveles de voltaje                       | 29 |

| Figura 3.2  | Algoritmo de ordenamiento de los SMs según su nivel de voltaje                 | 30 |

| Figura 3.3  | Diagrama de flujo                                                              | 30 |

| Figura 3.4  | Circuito de un MMC de una fase hecho en Simulink                               | 31 |

| Figura 3.5  | Simulación de medio puente                                                     | 32 |

| Figura 3.6  | Brazo superior                                                                 | 33 |

| Figura 3.7  | Interior de un SM hecho en Simulink: a) SPDT y b) Transistores                 | 34 |

| Figura 3.8  | Señal $V_{tri}$ , Señal PWM, algoritmo propuesto y Medición de voltaje y       |    |

|             | corriente                                                                      | 34 |

| Figura 3.9  | Señal de voltaje triangular                                                    | 35 |

| Figura 3.10 | Señales triangulares                                                           | 36 |

| Figura 3.11 | Generación del PWM                                                             | 37 |

| Figura 3.12 | Señales de disparo                                                             | 38 |

| Figura 3.13 | Bloque de medición voltaje y corriente                                         | 38 |

| Figura 3.14 | Algoritmo Propuesto o Control Balanceado                                       | 39 |

| Figura 3.15 | Algoritmo de Control Balanceado propuesto                                      | 40 |

| Figura 3.16 | Gráfica de los voltajes de los capacitores                                     | 41 |

| Figura 3.17 | Gráfica de la posición vectorial de cada capacitor                             | 41 |

| Figura 3.18 | Medición de la corriente                                                       | 42 |

| Figura 3.19 | Comparador de la posición vectorial de los capacitores contra la corriente     |    |

|             | total del arm-Upper                                                            | 43 |

| Figura 3.20 | Principio del XOR                                                              | 43 |

| Figura 3.21 | XOR                                                                            | 44 |

| Figura 3 22 | Inversor Multinivel Trifásico                                                  | 45 |

| Figura 3.23 | Los Voltajes de las 3 Fases                                         | 46 |

|-------------|---------------------------------------------------------------------|----|

| Figura 3.24 | Los voltajes del MMC trifásico                                      | 47 |

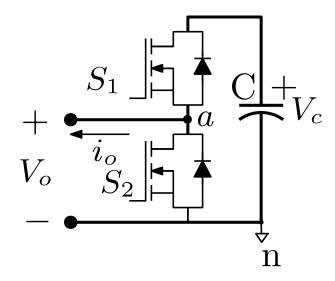

| Figura 4.1  | Diagrama esquemático de una celda o SM                              | 50 |

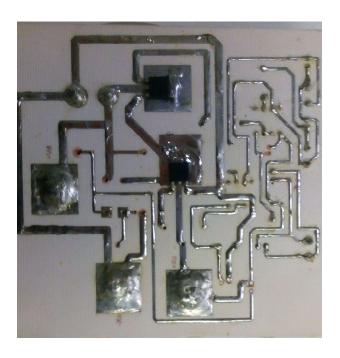

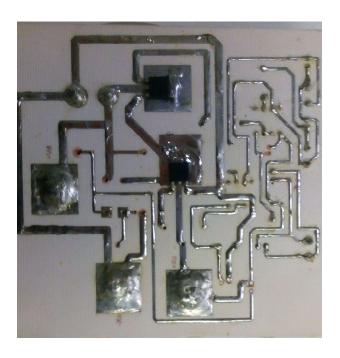

| Figura 4.2  | Foto de un SM con configuración de medio puente (HB)                | 50 |

| Figura 4.3  | Foto de un SM de la cara inferior mostrando los MOSFETs             | 51 |

| Figura 4.4  | Estado de conmutación para $S_1 = OFF, S_2 = OFF$ del SM            | 52 |

| Figura 4.5  | Estado de conmutación para $S_1 = OFF$ , $S_2 = ON$ del SM          | 52 |

| Figura 4.6  | Estado de conmutacón para $S_1=ON,S_2=OFF$ del SM                   | 53 |

| Figura 4.7  | Estado prohibido $S_1 = ON$ , $S_2 = ON$ del SM                     | 53 |

| Figura 4.8  | Esquema para analizar el funcionamiento del inversor multinivel     | 54 |

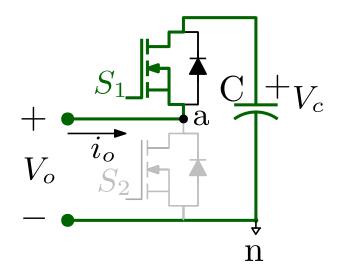

| Figura 4.9  | Foto de los 4 SM                                                    | 55 |

| Figura 4.10 | Esquema para analizar el funcionamiento del estado de conmutación 1 |    |

|             | del inversor multinivel                                             | 56 |

| Figura 4.11 | Esquema para analizar el funcionamiento del estado de conmutación 2 |    |

|             | del inversor multinivel                                             | 57 |

| Figura 4.12 | Esquema para analizar el funcionamiento del estado de conmutación 3 |    |

|             | del inversor multinivel                                             | 58 |

| Figura 4.13 | Esquema para analizar el funcionamiento del estado de conmutación 4 |    |

|             | del inversor multinivel                                             | 59 |

| Figura 4.14 | Esquema para analizar el funcionamiento del estado de conmutación 5 |    |

|             | del inversor multinivel                                             | 60 |

| Figura 4.15 | Esquema para analizar el funcionamiento del inversor multinivel     | 61 |

| Figura 4.16 | Foto de los 6 SMs                                                   | 62 |

| Figura 4.17 | Esquema para analizar el funcionamiento del estado de conmutación 1 |    |

|             | del inversor multinivel                                             | 63 |

| Figura 4.18 | Esquema para analizar el funcionamiento del estado de conmutación 2 |    |

|             | del inversor multinivel                                             | 64 |

| Figura 4.19 | Esquema para analizar el funcionamiento del estado de conmutación 3 |    |

|             | del inversor multinivel                                             | 65 |

| Figura 4.20 | Esquema para analizar el funcionamiento del estado de conmutación 4 |    |

|-------------|---------------------------------------------------------------------|----|

|             | del inversor multinivel                                             | 66 |

| Figura 4.21 | Esquema para analizar el funcionamiento del estado de conmutación 5 |    |

|             | del inversor multinivel                                             | 67 |

| Figura 4.22 | Esquema para analizar el funcionamiento del estado de conmutación 6 |    |

|             | del inversor multinivel                                             | 68 |

| Figura 4.23 | Esquema para analizar el funcionamiento del estado de conmutación 7 |    |

|             | del inversor multinivel                                             | 69 |

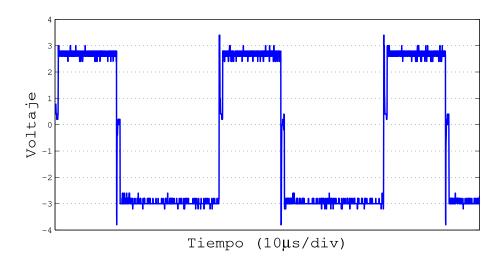

| Figura 5.1  | Señal de un SM carga R                                              | 72 |

| Figura 5.2  | Señal de un SM carga RL                                             | 72 |

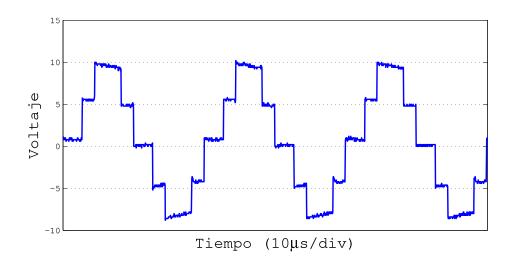

| Figura 5.3  | Señales $V_o$ de 5 niveles                                          | 73 |

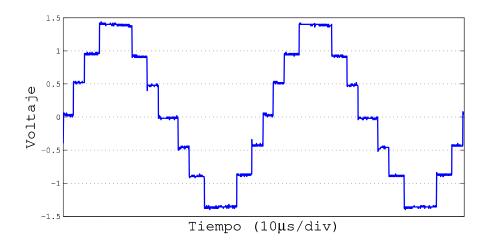

| Figura 5.4  | Señal de salida de 7 niveles                                        | 74 |

# Capítulo

# Introducción

En este Capítulo se aborda el tema de los convertidores multinivel, en la topología del convertidor modular multinivel (MMC del inglés, Modular Multilevel Converter) se componen por: submódulos (SMs) o celdas del módulo bidireccional múltinivel en cascada, conectadas en serie con un inductor buffer en cada pierna o fase. Cada SM está compuesto por la configuración de medio puente (HB), en el HB se compone por dos MOSFETs como elemento de conmutación y un capacitor de almacenamiento, en particular el convertidor modular multinivel [1], cuyo fin es convertir un voltaje de entrada de corriente directa (c.d.) a un voltaje simétrico de salida de corriente alterna (c.a.), controlado en magnitud y frecuencia deseada. Esta nueva topología ha tomado mucha popularidad en recientes años como una alternativa muy importante en el área de alta potencia y media tensión [1]. Para llevar a cabo esta tarea de conversión, los inversores tradicionales de dos niveles son ampliamente utilizados, pero presentan algunas desventajas como: las pérdidas por conmutación y la necesidad de grandes filtros para extraer la componente fundamental. Para enmendar estos problemas se han desarrollado tecnologías multinivel como el inversor de diodo anclado, el inversor de capacitor flotante y, por último, el inversor de fuentes independientes en cascada. La característica principal de este inversor de fuentes independientes en cascada es la capacidad de alto voltaje con dispositivos de voltaje limitado, baja distorsión armónica (THD), menor pérdida de conmutación, eficiencia alta, buena compatibilidad electromagnética, la facilidad de distribución y el encapsulado para optimizar el circuito ya que cada nivel de voltaje tiene la misma estructura. Se pueden usar técnicas de conmutación suaves para reducir las pérdidas por conmutación y la eliminación de filtros en la salida. Por otro lado, algunas de las desventajas son: la necesidad de fuentes de c.d. para cada inversor, al incrementar el número de niveles, se vuelve más complejo el control de voltaje.

El MMC se alimenta con una fuente de c.d. o dos y aparece el inconveniente en esta topología, al verse desbalanceado el voltaje de los capacitores de cada submódulo, provoca una desestabilización. A continuación, se presenta la propuesta de diseño y ejecución de un algoritmo, para que regule el voltaje, con el fin de un control de cada subrama del convertidor multinivel.

### 1.1. Antecedentes

Los inversores de voltaje convierten la energía proveniente de una fuente de c.d. de entrada a un voltaje de c.a. controlado de salida en magnitud, frecuencia y fase. Los inversores de potencia son empleados en automóviles, sistemas de c.a. que se alimentan con la energía de una batería, energías alternas, por ejemplo, de los aerogeneradores, de los paneles solares [2].

Tradicionalmente, para aplicaciones industriales son empleados los inversores de potencia de dos niveles, sin embargo, tienen algunas desventajas como las pérdidas por conmutación que depende del tipo de modulación y la necesidad de grandes filtros, debido a su alto contenido armónico. Para solventar algunos inconvenientes se han propuesto topologías de inversores multinivel como la del capacitor flotante y la del diodo anclado. Estos inversores multinivel tienen la limitante de [2]:

- 1. Sólo generar hasta 3 niveles sin que se presenten problemas de desequilibrio en el inversor.

- 2. Si se usa más de tres niveles se presenta el problema de desequilibrio en el voltaje de los capacitores.

- 3. Un control más complejo, así como también un alto nivel de distorsión armónica total (THD).

Recientemente, se han propuesto tecnologías de convertidor modular multinivel (MMC del inglés, Modular Multilevel Converter) para mitigar las desventajas de los inversores convencionales ya mencionados. Algunas ventajas de los MMCs son: teóricamente, no tienen la limitante en cuanto al número de niveles debido a que se pueden conectar más submódulos; se reduce el filtro de salida; y facilidad en el control desde el punto de vista del sistema de potencia. Sin embargo, el MMC presenta algunos inconvenientes como: al incrementarse el número de niveles, el control de voltaje se vuelve más complejo; el número de semiconductores aumenta, no obstante con capacidades de potencia menores, la magnitud por nivel es constante [2].

## 1.2. Planteamiento del problema

Considerando que los MMCs se pueden modular a frecuencia de línea, 60 Hz por ejemplo, o a alta frecuencia con una señal PWM, los voltajes de los capacitores de cada submódulo se pueden ver desbalanceados, lo cual provocaría una desestabilización del inversor. El problema se incrementa cuando la frecuencia de conmutación es menor, por lo cual se requiere una estrategia de control que combine una técnica de modulación, lo cual permita el balanceo y el control de los voltajes [1] - [3].

Por lo tanto, se puede establecer que es necesaria una estrategia de modulación, por lo cual permita mantener el voltaje estable de los capacitores de cada submódulo mediante un algoritmo de balanceo de voltaje y ordenamiento de la magnitud de los voltajes, con el fin de poder sintetizar un voltaje de c.a. con niveles constantes, dentro de un rango de regulación, eliminando así la necesidad de un filtro para reducir el THD y también reducir las pérdidas por conmutación aplicando técnicas multinivel.

## 1.3. Propuesta de solución

Con el fin de sintetizar un voltaje de c.a. con niveles constantes se propone utilizar una técnica de modulación escalonada que permita la corrección de los voltajes en los capacitores, lo cual provocará que se reduzca el THD y esto beneficiará la calidad en el voltaje de salida porque se logrará tener una topología modular con la posibilidad de incrementar fácilmente el número de niveles. Es posible la creación de este algoritmo basado en un ordenamiento por comparación es decir se puede tener un control local para cada submódulo del convertidor multinivel.

### 1.4. Justificación

Se requiere diseñar e implementar un algoritmo para el control en los voltajes de los capacitores que cumpla con las características de desempeño deseadas de velocidad y precisión, con el fin de mantener un voltaje controlable en la salida del inversor multinivel.

# 1.5. Objetivo general

Diseñar e implementar un inversor MMC monofásico con un algoritmo de control para el balanceo de los voltajes en los capacitores.

#### 1.5.1. Objetivos específicos

- Simulación del inversor monofásico con todos sus componentes.

- Diseño del inversor trifásico.

- Desarrollar un algoritmo de balanceo y ordenamiento de los voltajes en los capacitores.

- Implementar el algoritmo.

- Programa de control maestro en el microcontrolador.

# 1.6. Hipótesis

Empleando un algoritmo de control basado en un ordenamiento por comparación se puede tener un control local para cada subrama en el inversor multinivel y de esta forma la tarea de regulación se ataca localmente, siendo controlada por un microcontrolador maestro.

### 1.7. Alcances y limitaciones

#### **1.7.1.** Alcance

- Implementación de un algoritmo de un inversor de puente completo H.

- Implementación de un algoritmo para el control del voltaje en los submódulos.

- Construcción de un prototipo de menor potencia (100W) para validación experimental.

- Programación del control maestro.

- Diseño del sistema modular.

# 1.7.2. Limitaciones

- Inversor bajo estudio de tipo monofásico.

- Número de niveles del prototipo experimental limitado a siete.

# 1.8. Conclusión

En el primer Capítulo se declaró, como propósito principal el diseño e implementación de un inversor MMC ya que es una topología que tomó mucha fuerza en los últimos años, existen los inversores de dos niveles que ya son usados en la industria, pero tienen algunas desventajas, por eso surgió una nueva topología multinivel como el capacitor flotante y el diodo anclado para algunas de estas desventajas sean solucionadas. En los últimos años fue propuesto un inversor multinivel con fuentes independientes ya que no presenta la limitación de los niveles porque se agregan más submódulos y se reduce el filtro en la salida, sin embargo se presentan algunas limitaciones en esta nueva topología como son: al incrementar el número de niveles se hace más complejo, perdiendo practicidad. Sin embargo, pierde practicidad al aumentar el número de niveles; transistores, el cual el control se hace más complejo.

Al ser mayor el número de niveles que se desea generar, el voltaje de los capacitores de cada submódulo se empiezan a desbalancear, ya que causa inestabilidad en el inversor, por lo cual se propone la creación de un algoritmo de control que regule el voltaje de los capacitores de cada submódulo, la elaboración de dicho algoritmo, se basará en un ordenamiento por comparación para controlar cada subrama del inversor multinivel y de esta forma la regulación de los voltajes en los capacitortes se ataca localmente, siendo regido por un microcontrolador maestro.

# Capítulo

# Marco teórico

En este Capítulo se desarrollan las bases teóricas que permitirán conocer los conceptos básicos de la topología multinivel, con el fin de poder alcanzar el objetivo de diseñar un algoritmo de regulación para la implementación de un inversor multinivel.

En primer lugar, se partirá con una breve descripción del inversor con el fin de comprender su principio de operación. Después, se dará una clasificación de los inversores multinivel empezando con el número de niveles, el tipo de sistema, su topología y por último su tipo de modulación, también en esta clasificación se mencionarán las topologías multinivel. No obstante, en este trabajo se enfocará en la topología de inversores con fuentes independientes. Posteriormente, se describirá el inversor multinivel y se dará una definición de su uso. Cabe mencionar que la función principal del inversor es sintetizar un voltaje de salida de c. a. a partir de varios niveles de voltaje de c.d. de entrada, ya que estos voltajes, al ser sumados, se produce en la salida una onda escalonada, semejante a una senoidal pura. Por otro lado, esto garantiza la reducción de THD o contaminación armónica y reduce las pérdidas de conmutación, esta es una gran opción para la conversión de energías de c.d. a c.a. porque tiene una alta eficiencia. Además, en la actualidad los inversores multinivel son una gran opción para la industria, a causa de ser los más adecuados para aplicaciones de media tensión y alta potencia.

Por otra parte se explicará el análisis de los estados de conmutación de una celda o submódulo (SM), es decir, si el submódulo está participando en generar un nivel de voltaje al estar insertado o si el SM se encuentra en modo baipás y también se hablará de los tipos de modulación que existen para el control del inversor como; modulación de ancho de pulso (PWM), modulación de ancho de pulso senoidal (SPWM), modulación vector espacial (SVM), y por otro lado, se explican a detalle los algoritmos de ordenamiento que existen en la actualidad y por último, una descripción de los MMC monofásico y trifásico.

# 2.1. Descripción del inversor

Los convertidores de c.d. a c.a. se conocen como inversores [4]. Su objetivo principal es modificar un voltaje de entrada de c.d. a un voltaje simétrico de salida de c.a. con una magnitud y una frecuencia deseadas. Tanto el voltaje como la frecuencia puede ser fijo o variables [4]. Un voltaje variable de salida se puede obtener modificando el voltaje de entrada de c.d., manteniendo constante la ganancia del inversor. Por otro lado, si el voltaje de c.d. de entrada es fijo y no puede ser controlado, se puede obtener un voltaje variable de salida haciendo variar la ganancia del inversor, lo que se consigue normalmente por modulación de ancho de pulso (PWM) dentro del inversor. La ganancia del inversor se puede definir como la relación entre el voltaje de salida de c.a. y el voltaje de entrada de c.d. [4].

### 2.2. Clasificación de los inversores

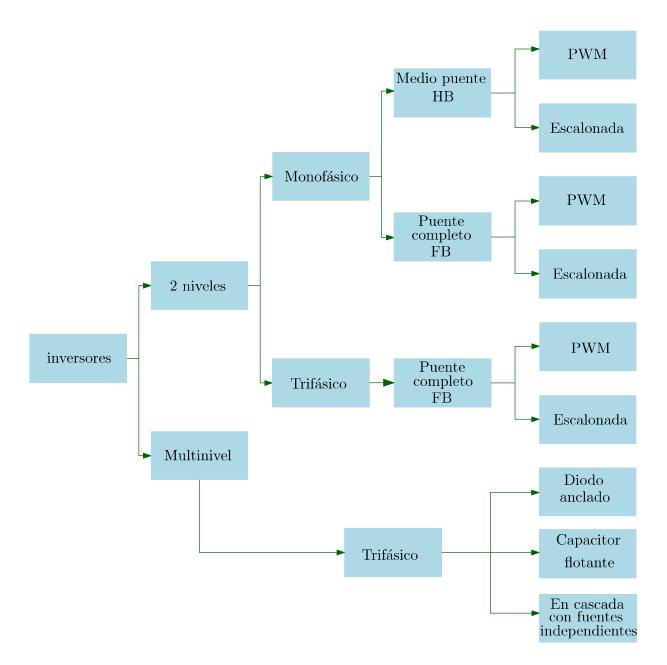

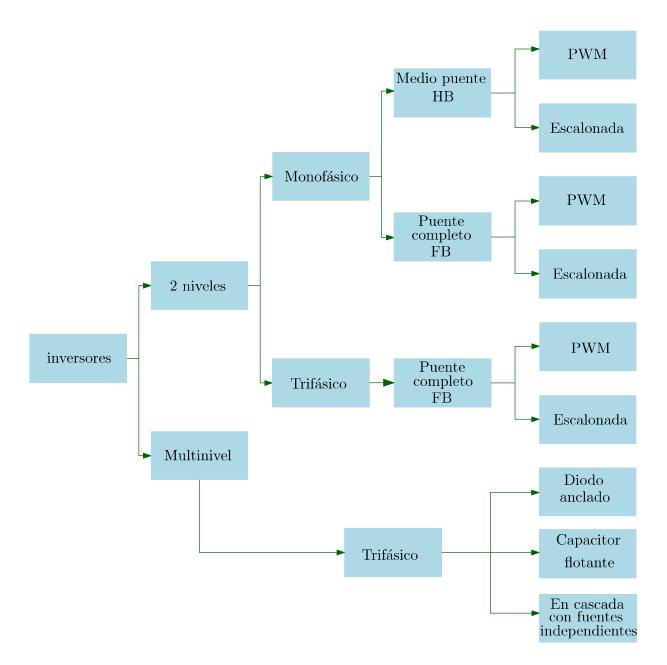

En la Figura 2.1 se observa una clasificación de los inversores de 2 niveles y multinivel, en esta clasificación que incluye el tipo de inversor, el tipo de sistema, su topología y por último su modulación [5].

Figura 2.1: Clasificación de los inversores.

# 2.3. Descripción del Inversor multinivel

La función principal de los inversores multinivel es la de sintetizar una tensión de salida a partir de varios niveles de tensión de c.d. de entrada. La conformación de la forma de onda en la salida es dependiente del número de niveles entregados por las fuentes de voltaje, produciendo una salida escalonada que se aproxima a la señal sinusoidal deseada, lo que garantiza un contenido armónico y pérdidas por conmutación menores. En la actualidad, los inversores multinivel se consideran como los convertidores de potencia con mayor demanda de utilización en la industria, por ser los más adecuados para aplicaciones donde se requiera media tensión y alta potencia [6].

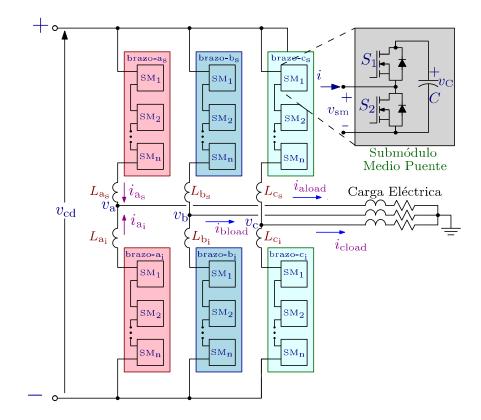

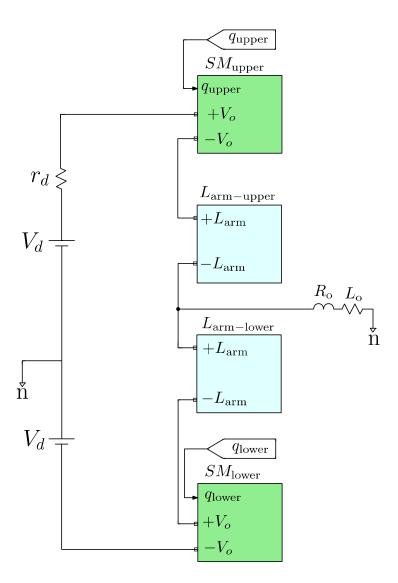

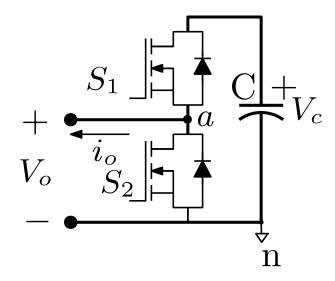

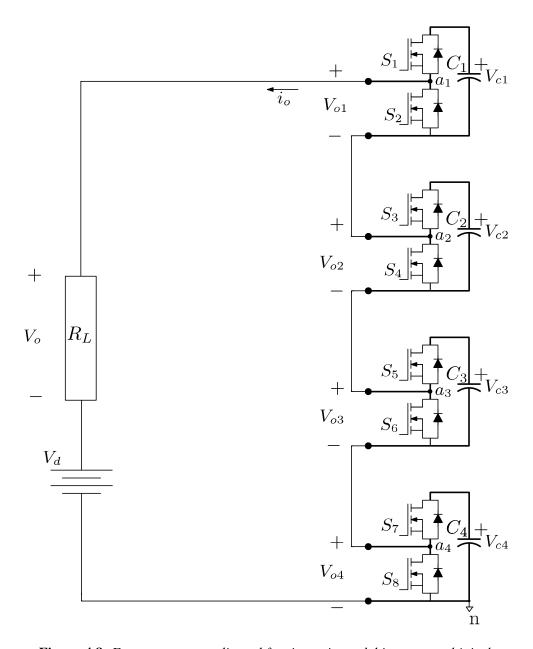

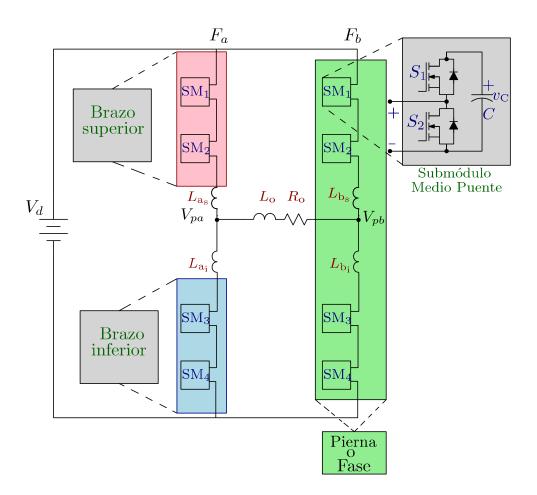

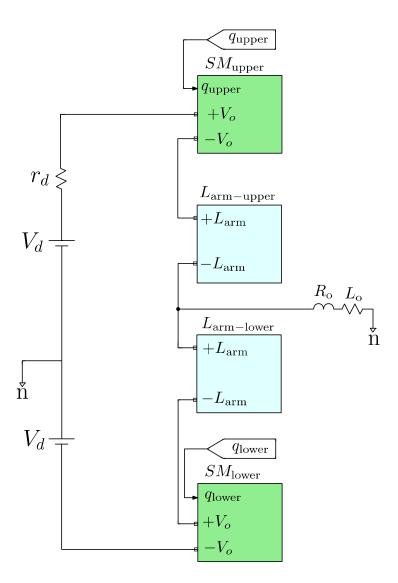

#### 2.3.1. Topología del MMC

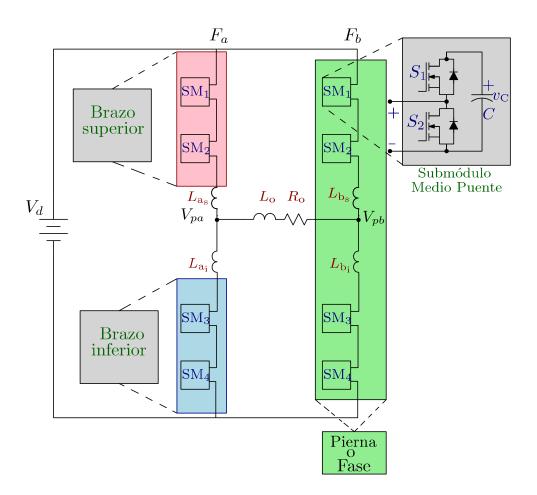

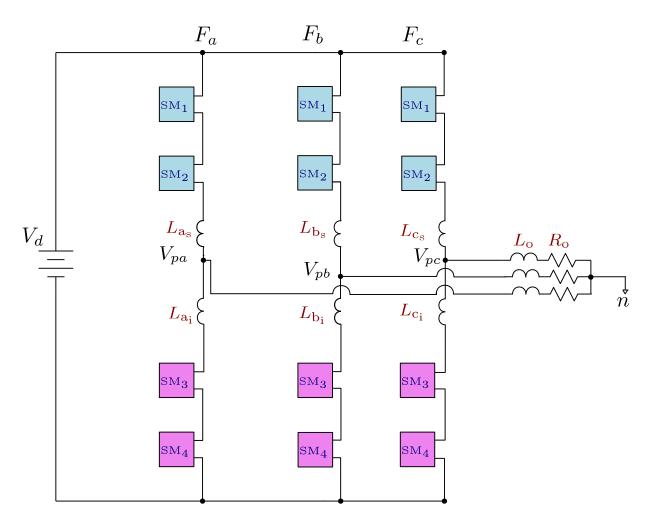

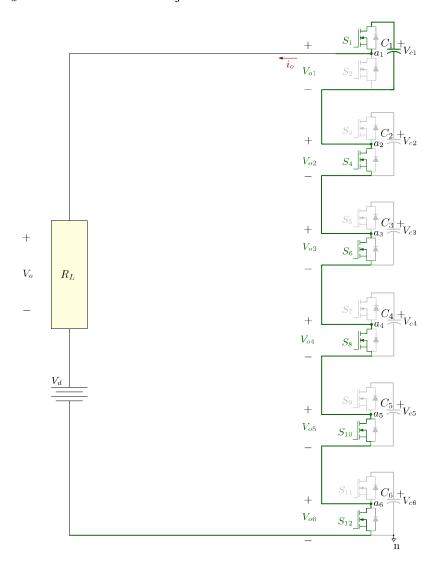

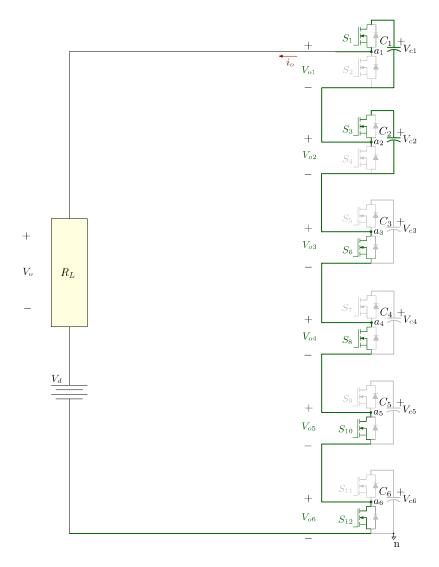

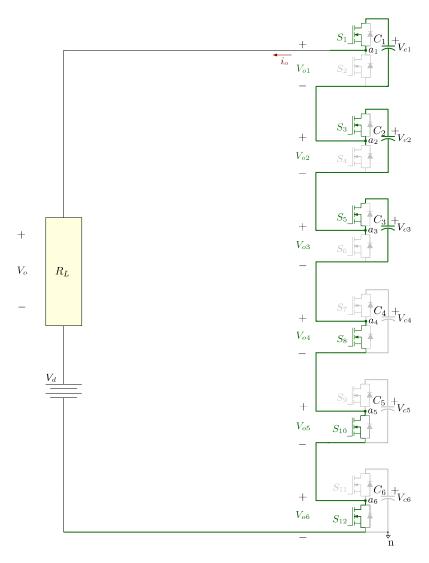

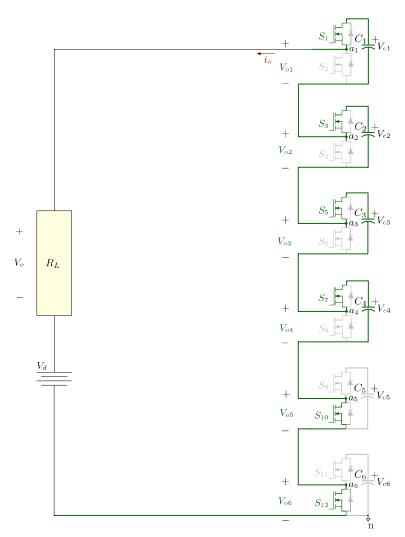

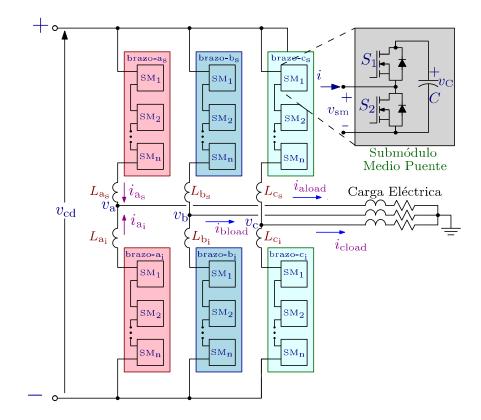

En la Fig. 2.2 se muestra un diagrama detallado de un convertidor modular multinivel (MMC) con una carga trifásica RL y un voltaje de alimentación de  $v_{cd}$  en la entrada. En este circuito se observan tres piernas o fases, en cada pierna se incluye un brazo superior y un brazo inferior, todos los brazos superiores se definen como brazo-a<sub>s</sub>, brazo-b<sub>s</sub>, brazo-c<sub>s</sub> y para los brazos inferiores se les denominan brazo-a<sub>i</sub>, brazo-b<sub>i</sub>, brazo-c<sub>i</sub>. Cada brazo se conforma por una celda conectada en serie con otra, se podrán conectar hasta n celdas, cada celda es llamada submódulo (SM). Internamente cada SM está compuesto por un par de transistores conectados en serie y en paralelo un capacitor de almacenamiento que en, conjuntó forman la configuración de medio puente (HB, del inglés half-bridge) o un puente completo (FB, del inglés full-bridge) [7] - [8] - [9].

La diferencia de emplear un HB y un FB se refleja en la cantidad de estados de conmutación permitidos, cada uno está compuesto por m transistores conectados en serie y fuentes independientes conectados cada uno, la configuración HB tiene 2 transistores por brazo mientras que la FB el doble por cada brazo.

Figura 2.2: Diagrama de un MMC con una carga trifásica RL.

En el diagrama que se muestra en la Fig.2.2 se usan HBs en cada SM. Los inductores  $L_{\rm as}$ ,  $L_{\rm bs}$ ,  $L_{\rm cs}$ ,  $L_{\rm ai}$ ,  $L_{\rm bi}$ ,  $L_{\rm ci}$  cumplen con la función de reducir las corrientes circulantes provocadas por las pequeñas diferencias entre el voltaje de alimentación y el voltaje de cada submódulo. En la Tabla 2.1 se definen las variables restantes de la Figura 2.2.

**Tabla 2.1:** Variables empleadas en el MMC.

| Variables del inversor                                                  |                                        |  |

|-------------------------------------------------------------------------|----------------------------------------|--|

| $v_{ m a}, v_{ m b}, v_{ m c}$ Voltajes de fase                         |                                        |  |

| $i_{\rm as},i_{\rm bs},i_{\rm cs}$                                      | Corrientes de cada fase brazo superior |  |

| $i_{ m ai},i_{ m bi},i_{ m ci}$                                         | Corrientes de cada fase brazo inferior |  |

| $i_{ m a_{load}}, i_{ m b_{load}}, i_{ m c_{load}}$ Corrientes de carga |                                        |  |

Al emplear FBs no se incrementa el número de niveles en relación con un MMC con la misma cantidad de HBs. Dependiendo del tipo de SM empleado, la forma de onda del voltaje

sintetizado puede ser de dos o tres niveles [9].

En (2.1) y (2.2) se tiene una descripción matemática de los brazos del MMC de una sola fase, en (2.1) se encuentra el modelo matemático del brazo superior del inversor y en (2.2) se tiene el modelo matemático del brazo inferior del inversor. Estos modelos se obtienen usando la LVK Ley de Voltaje de Kirchhoff que se aplica individualmente a cada brazo, tomando la trayectoria desde el bus de c.d. con dirección a la carga.

$$\frac{V_{dc}}{2} - \sum_{j=1}^{N} V_{SM_{as}} - L_{as} \frac{\mathrm{d}i_{as}}{\mathrm{d}t} - r_{as}i_{as} = V_{as}$$

(2.1)

$$-\frac{V_{dc}}{2} + \sum_{j=N+1}^{2N} V_{SM_{is}} + L_{ai} \frac{\mathrm{d}i_{ai}}{\mathrm{d}t} + r_{ai}i_{ai} = V_{ai}$$

(2.2)

## 2.4. Análisis de un SM con configuración HB

Cada SM se constituye por dos MOSFETs que se encuentran conectados en serie y un capacitor de almacenamiento en paralelo, cada SM pueden generar hasta dos niveles en las terminales de salida  $V_o$ , se conectan en serie para obtener cierto número de niveles, ya que al sumar todos los niveles, se genera una señal escalonada, es decir, que se semeja a una onda senoidal pura.

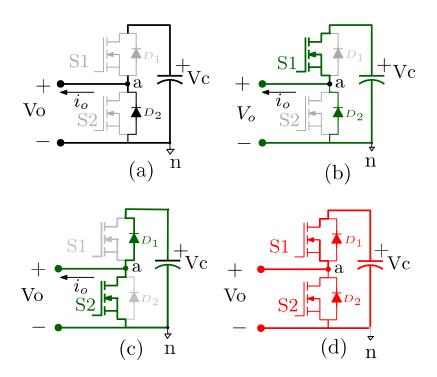

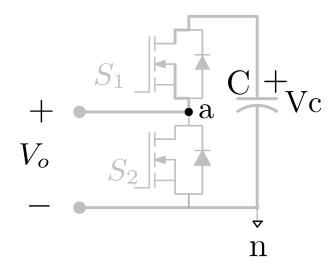

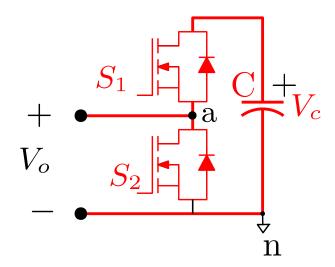

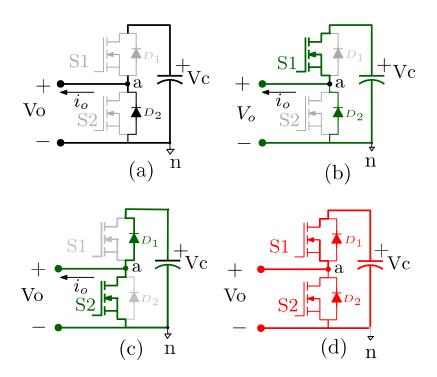

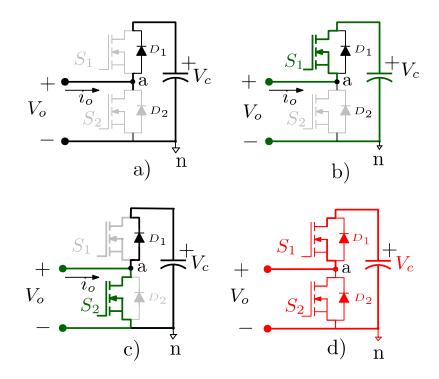

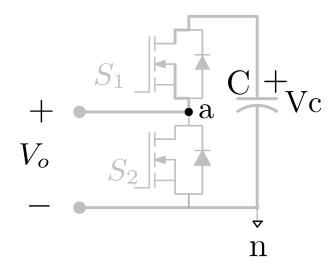

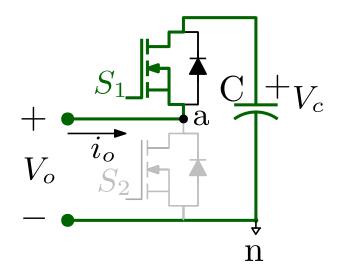

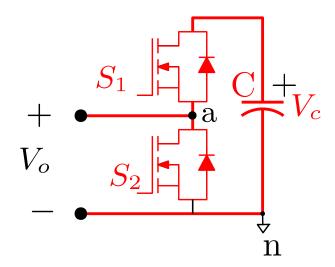

En las Figura 2.3 y Figura 2.4 se observan cuatro estados de conmutación del SM. El primer caso se verá en la Figura 2.3, el sentido de la corriente está saliendo del SM ( $i_o < 0$ ), en la Figura 2.4 se muestra el segundo caso cuando la corriente está entrando al SM ( $i_o > 0$ ). Estos estados serán explicados a continuación.

Caso 1:

$$(i_o < 0)$$

1. En la Figura 2.3a se muestra el estado de conmutación cuando están apagados ( $S_1 = OFF$ ;  $S_2 = OFF$ ), por lo tanto en este estado el voltaje de salida es cero y por último el diodo  $D_1$  está bloqueado esto quiere decir que no cierra el circuito para conectar el

- capacitor y el diodo  $D_2$  se encuentra conduciendo, esto ocasiona que la corriente pase a través de  $D_2$ .

- 2. En la Figura 2.3b se observan los estados de conmutación de  $(S_1 = ON; S_2 = OFF)$ ,  $S_1$  está encendido en consecuencia está conectando el capacitor que  $V_o$  estará en las terminales de salida, además el diodo  $D_1$  se encuentra bloqueado y para  $S_2$  se encuentra apagado y su diodo  $D_2$  se encuentra en paralelo con el capacitor.

- 3. Para la Figura 2.3c se ven los estados  $(S_1 = OFF; S_2 = ON)$ ,  $S_1$  está apagado y el diodo  $D_1$  se está conactando en paralelo con el capacitor y para  $S_2$  se encuentra encendido por lo tanto en las terminales de salida se obtienen un voltaje de 0 V y por último el diodo  $D_2$  está bloqueado.

- 4. En la Figura 2.3d cuando  $(S_1 = ON; S_2 = ON)$  están encendidos al mismo tiempo, se ve un cortocircuito (C.C), esto no es permitido por lo cual es un estado prohibido.

**Figura 2.3:** Estados básicos de conmutación de un SM con  $(i_o < 0)$ .

En la Tabla 2.2 se muestran los voltajes de salida y sus estados de conmutación de la Figura 2.3.

| <b>Tabla 2.2:</b> | Estados de | conmutación de | un SMs i | para $(i_0 < 0)$ . |

|-------------------|------------|----------------|----------|--------------------|

|                   |            |                |          |                    |

| $S_1$ | $S_2$ | $V_o$ |

|-------|-------|-------|

| 0     | 0     | 0     |

| 0     | 1     | 0     |

| 1     | 0     | $V_c$ |

| 1     | 1     | C.C   |

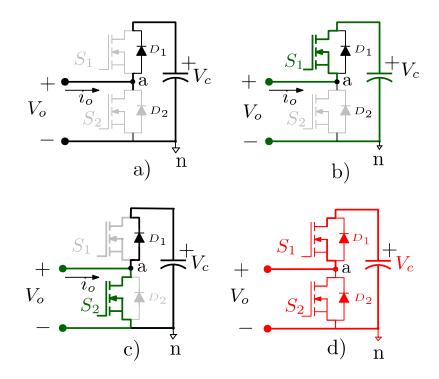

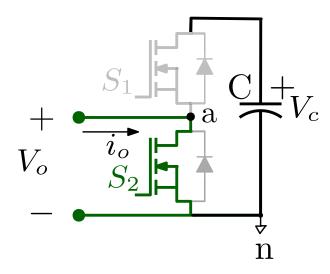

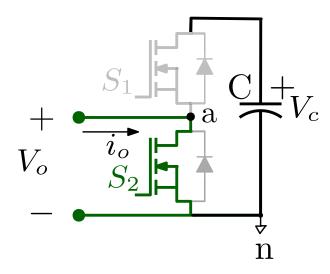

Caso 2:  $(i_o > 0)$

En este caso el flujo de corriente está entrando al SM como se muestra en la Figura 2.4 es la misma figura que fue mostrada anteriormente.

**Figura 2.4:** Estados básicos de conmutación de un SM con  $(i_o > 0)$ .

1. En la Figura 2.4a se muestra el estado de conmutación cuando están apagados  $(S_1 = OFF; S2 = OFF)$ , por lo tanto en este estado el voltaje de salida es  $V_0$  y el diodo  $D_1$

está conduciendo, esto ocasiona que el diodo se conecte al capacitor y la corriente pase a través de  $D_1$  al capacitor y el diodo  $D_2$  se encuentra bloqueado, esto quiere decir, que no cierra el circuito.

- 2. En la Figura 2.4b se observan los estados de conmutación cuando  $(S_1 = ON; S_2 = OFF)$ ,  $S_1$  está encendido y el diodo  $D_1$  se encuentra conduciendo, el voltaje en terminales es  $V_o$  y  $S_2$  está apagado y por último el diodo  $D_2$  se encuentra apagado.

- 3. En la Figura 2.4c se ve que  $(S_1 = OFF; S_2 = ON)$ ,  $S_1$  está apagado y su diodo  $D_1$  se encuentra conectado en paralelo con el capacitor y en las terminales de salida de  $V_o$  su voltaje es cero y  $S_2$  se encuentra encendido y su diodo  $D_2$  no conduce.

- 4. En la Figura 2.4d se observan que ( $S_1 = ON$ ;  $S_2 = ON$ ) se encuentran encendidos y esto ocasiona un cortocircuito (C.C) en la fuente, ya que no se puede poner ambos transistores a la vez, este estado es prohibido.

**Tabla 2.3:** Estados de conmutación de un SMs para  $(i_o > 0)$ .

| $S_1$ | $S_2$ | $V_o$ |

|-------|-------|-------|

| 0     | 0     | $V_c$ |

| 0     | 1     | 0     |

| 1     | 0     | $V_c$ |

| 1     | 1     | C.C   |

En las siguientes tablas se observan los estados de descarga y carga de los capacitores de almacenamiento de cada SM y la dirección de la corriente. En las Tablas 2.4 y 2.5 se ven los estados de conmutación y la dirección de la corriente por lo cual, conociendo la dirección de la corriente, se puede saber si el capacitor se está cargando o descargando, es decir, si la corriente  $(i_o>0)$  el capacitor se encuentra cargandose  $(\Delta V_c>0)$ , si la corriente  $(i_o<0)$  el capacitor se encuentra insertado en pocas palabras el estado del capacitor se encuentra en descarga  $(\Delta V_c<0)$ .

En la Tabla 2.4 se observa en cuál estado de conmutación se está cargando el capacitor ya

que la polaridad de la corriente está entrando hacia el capacitor en consecuencia el voltaje  $\Delta V_c$  es menor, porque el capacitor se encuentra cargando.

#### SM insertado:

- Siempre que  $(i_o>0)$  la carga en el capacitor aumentará y por ende también el voltaje presente.

- Cuando la corriente sea negativa, es decir, salga del SM, la carga en el capacitor decrecerá provocando que el voltaje también disminuya.

**Tabla 2.4:** Estados de conmutación, dirección de la corriente y el estado de carga del capacitor para  $(i_0 > 0)$ .

| $S_1$ | $S_2$ | $i_o$ | $\Delta V_c$ | $V_o$ |

|-------|-------|-------|--------------|-------|

| 0     | 0     | Entra | >0           | $V_c$ |

| 0     | 1     | Entra | >0           | 0     |

| 1     | 0     | Entra | >0           | $V_c$ |

En la Tabla 2.5 se muestra en cuál estado se descarga el capacitor, debido a que la dirección de la corriente sale del inversor en pocas palabras el voltaje del capacitor  $\Delta V_c$  es alto y se inserta para ser descargado.

#### SM no insertado:

lacktriangle Si el SM se encuentra en estado baipás, sin importar el sentido de la corriente  $i_o$ , la carga en el capacitor se mantendrá sin cambio.

**Tabla 2.5:** Estados de conmutación, dirección de la corriente y el estado de carga del capacitor para  $(i_o < 0)$ .

| $S_1$ | $S_2$ | $i_o$ | $\Delta V_c$ | $V_o$ |

|-------|-------|-------|--------------|-------|

| 0     | 0     | Sale  | 0            | 0     |

| 0     | 1     | Sale  | 0            | 0     |

| 1     | 0     | Sale  | <0           | $V_c$ |

# 2.5. Tipos de modulación para multinivel

La forma de onda senoidal deseada es lograda por la variación del ciclo de trabajo sinusoidalmente con el tiempo empleando técnicas de modulación de ancho de pulso. Los métodos de control que generan el patrón necesario PWM pueden ser clasificados como [10]:

- 1. PWM senoidal (SPWM).

- 2. Eliminación selectiva de armónicos (SHEPWM).

- 3. PWM de rizado mínimo de corriente (MRCPWM).

- 4. PWM con control de corriente por banda de histéresis.

- 5. PWM de vector de espacio (SVM).

Dos conceptos pueden ser distinguidos en función de la variable controlada por el PWM: para aplicaciones de pequeña o mediana potencia, la corriente es controlada por un PWM ha probado ser ventajosa. En aplicaciones de gran potencia con baja frecuencia de conmutación, el control de voltaje es más ventajoso. Para sistemas de alta potencia es mejor la técnica SVM porque se basa en la representación de las cantidades trifásicas como vectores en un plano bidimensional. A continuación una breve explicación de la técnica SVM [10].

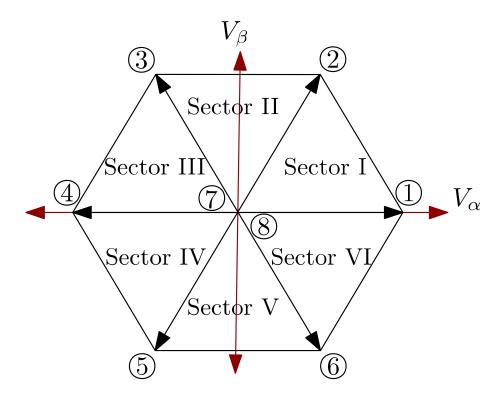

# 2.6. Modulación por vector espacial

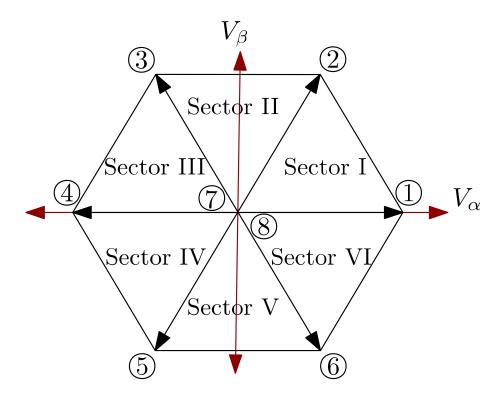

La modulación por vector espacial (SVM) es muy distinta de los métodos por PWM. Con la técnica PWM, se puede imaginar al inversor como tres etapas separadas de activación simétrica o en contra fase, cuales modelan cada onda de fase en forma independiente. Sin embargo, la técnica SVM maneja al inversor como una sola unidad; en forma específica, el inversor puede activarse con ocho estados únicos, como se ve en la Fig. 2.5. Sin embargo, entre estos estados hay 6 sectores activos y 2 sectores nulos. La modulación se obtiene por el estado de conmutación del inversor. Las estrategias de control se implementan con sistemas digitales [4].

La técnica SVM es un método de modulación digital, en la cual el objetivo es generar voltajes PWM en la línea de carga que en promedio son iguales a determinados voltajes de línea (o de referencia) de carga. Esto se hace en cada periodo de muestreo seleccionando en forma adecuada los estados de los interruptores del inversor y calculando el tiempo adecuado para cada estado. La selección de los estados y sus periodos se hacen con la transformación del vector espacial (SV) [4].

La matriz de transformación de  $\alpha$  y  $\beta$  o la transformación de Clarke como también se conoce, es la que se usa en la técnica SVM, esta modulación se basa en la representación de las cantidades trifásicas como vectores en un plano bidimensional ( $\alpha$ ,  $\beta$ ) [10]. El vector **B** son los vectores de voltaje de fase o de línea, la matriz **A** es la descomposición de los vectores desfasado  $120^{\circ}$  grados cada uno.

$$\mathbf{X}_{\alpha\beta} = \mathbf{A} \cdot \mathbf{B} \tag{2.3}$$

donde:

$$\mathbf{X}_{lphaeta} = egin{bmatrix} ec{V}_lpha \ ec{V}_eta \end{bmatrix}, \quad \mathbf{A} = egin{bmatrix} 1 & -rac{1}{2} & -rac{1}{2} \ 0 & -rac{\sqrt{3}}{2} & rac{\sqrt{3}}{2} \end{bmatrix}, \quad \mathbf{B} = egin{bmatrix} ec{V}_a \ ec{V}_b \ ec{V}_c \end{bmatrix}$$

**Figura 2.5:** Diagrama de los ocho vectores obtenidos a partir de la transformación  $\alpha$  y  $\beta$ .

La técnica SVM tiene las ventajas de reducir los armónicos y mayor índice de modulación, además de la posibilidad de implementación digital completa mediante un microcontrolador en un sólo circuito integrado. Por la flexibilidad de su manipulación, la técnica SVM tiene cada vez mayores aplicaciones en los convertidores de potencia y en la excitación de motores [4].

En los inversores trifásicos se suelen usar las técnicas de modulación sinusoidal, por inyección de armónicos y SVM. Por la flexibilidad de manipulación y la implementación digital, la SVM tiene aplicaciones crecientes en los convertidores de potencia y en la excitación de motores [4].

### 2.6.1. Fórmulas para calcular los niveles del inversor

El siguiente punto trata de implementar las fórmulas para saber el número de niveles de un inversor como también la matriz de transformación  $\alpha$  y  $\beta$  y por último las matrices de Fase y de Línea, se usará el circuito de la Figura 2.2, en cuanto a cómo determinar la cantidad de niveles de un MMC se muestran a continuación:

- 1. Número de niveles : n

- 2. Número de combinaciones distintas:  $n^3 n + 1$

- 3. Número total de combinaciones:  $n^3$

- 4. Número de niveles de línea-línea: 2n-1

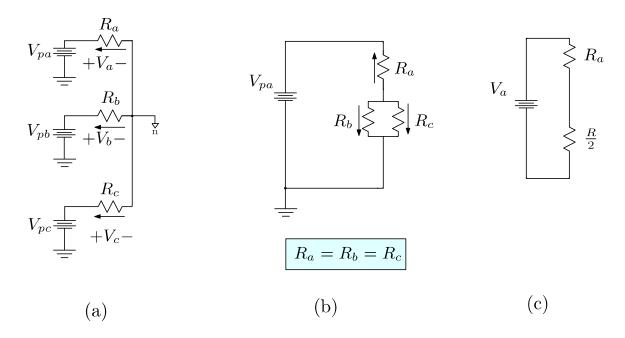

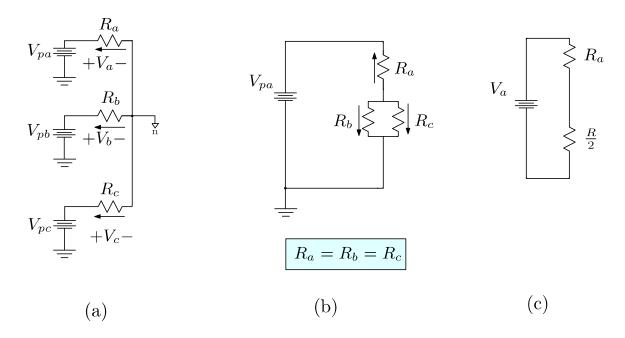

La matriz de voltajes de fase  $A_F$  se obtiene aplicando el Principio de Superposición en el circuito de la Fig. 2.6, en la Fig. 2.6a es el circuito original y en la Fig. 2.6b es el circuito equivalente aplicando el Principio de Superposición se apaga dos de las fuentes y se procede a resolverlo reduciendo el circuito y obteniendo un circuito equivalente como se muestra en la Fig. 2.6c por último se resuelve con un divisor de tensión, la matriz  $B_F$  son los voltajes de polo, la matriz  $X_F$  es la matriz de fase.

Figura 2.6: Circuito equivalente para el análisis de los voltajes de fase.

$$\mathbf{X}_{\mathbf{F}} = \mathbf{A}_{\mathbf{F}} \cdot \mathbf{B}_{\mathbf{F}} \tag{2.4}$$

donde  $X_F, A_F, B_F$ :

$$\mathbf{X_F} = egin{bmatrix} ec{V}_{an} \ ec{V}_{bn} \ ec{V}_{cn} \end{bmatrix}, \quad \mathbf{A_F} = egin{bmatrix} rac{2}{3} & -rac{1}{3} & -rac{1}{3} \ -rac{1}{3} & rac{2}{3} & -rac{1}{3} \ -rac{1}{3} & -rac{1}{3} & rac{2}{3} \end{bmatrix}, \quad \mathbf{B_F} = egin{bmatrix} ec{V}_{pa} \ ec{V}_{pb} \ ec{V}_{pc} \end{bmatrix}$$

Matriz de voltaje de línea-línea  $\mathbf{X}_{LL}$ , la matriz  $\mathbf{B}_{LL}$  es la matriz de voltajes de polos y la matriz  $\mathbf{A}_{LL}$  es la matriz de línea.

$$\mathbf{X}_{\mathbf{LL}} = \mathbf{A}_{\mathbf{LL}} \cdot \mathbf{B}_{\mathbf{LL}} \tag{2.5}$$

donde  $X_{LL}$ ,  $A_{LL}$ ,  $B_{LL}$  son:

$$\mathbf{X_{LL}} = egin{bmatrix} ec{V}_{ab} \ ec{V}_{bc} \ ec{V}_{ca} \end{bmatrix}, \quad \mathbf{A_{LL}} = egin{bmatrix} 1 & -1 & 0 \ 0 & 1 & -1 \ -1 & 0 & 1 \end{bmatrix}, \quad \mathbf{B_{LL}} = egin{bmatrix} ec{V}_{pa} \ ec{V}_{pb} \ ec{V}_{pc} \end{bmatrix}$$

Para obtener la matriz  ${\bf A_{LL}}$  se deben usar las ecuaciones de voltaje de línea, donde el conjunto de los voltajes en la (2.6) el valor de  $\vec{V_a} = \vec{V_b} = 1$  y  $\vec{V_c} = 0$ , en el (2.7)  $\vec{V_b} = \vec{V_c} = 1$  y  $\vec{V_a} = 0$ , y por último en el (2.8)  $\vec{V_c} = \vec{V_a} = 1$  y  $\vec{V_d} = 0$ .

$$\vec{V}_{ab} = \vec{V}_a - \vec{V}_b \tag{2.6}$$

$$\vec{V}_{bc} = \vec{V}_b - \vec{V}_c \tag{2.7}$$

$$\vec{V}_{ca} = \vec{V}_c - \vec{V}_a \tag{2.8}$$

# 2.7. Algoritmos de ordenamiento

En la actualidad existen diversos algoritmos de balanceo para regular los voltajes en los capacitores, su función principal es ordenar los voltajes en cada ciclo de conmutación y elegir quien se carga o se va a descargar según la dirección de la corriente del brazo. En estos algoritmos están basados en el algoritmo de la burbuja [17], en la literatura hay una gran variedad de ellos pero en el siguiente capítulo se dará una explicación más amplia de dichos algoritmos.

# 2.8. Inversor monofásico y trifásico de multinivel

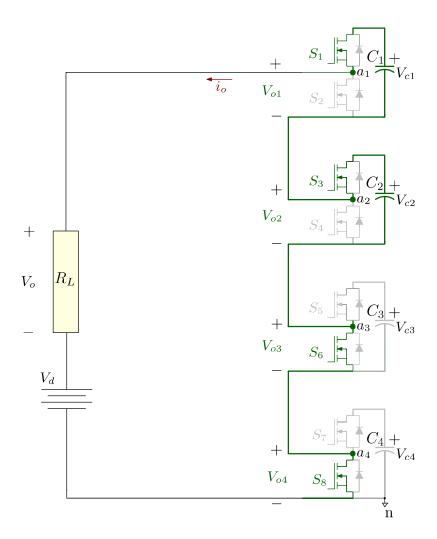

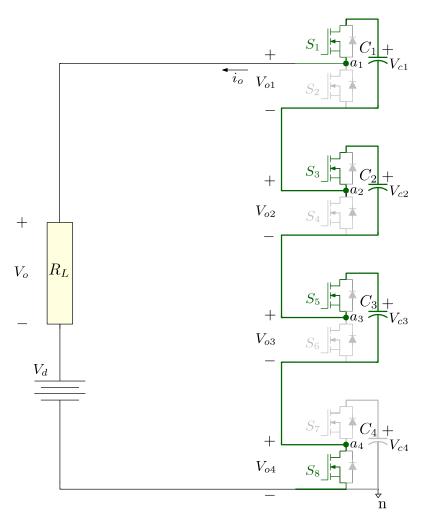

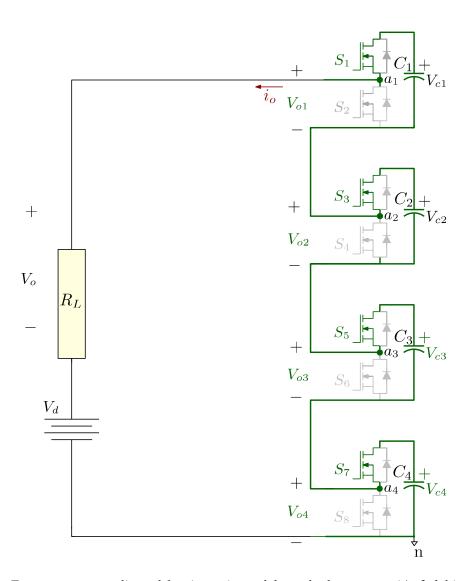

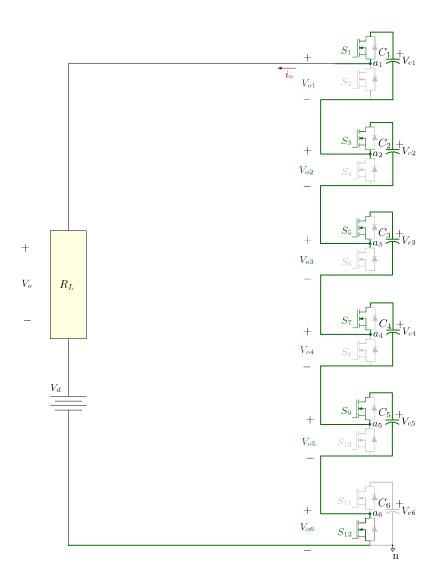

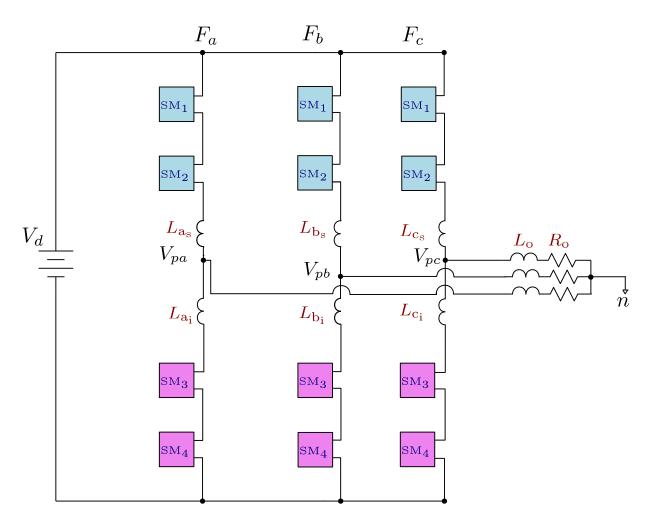

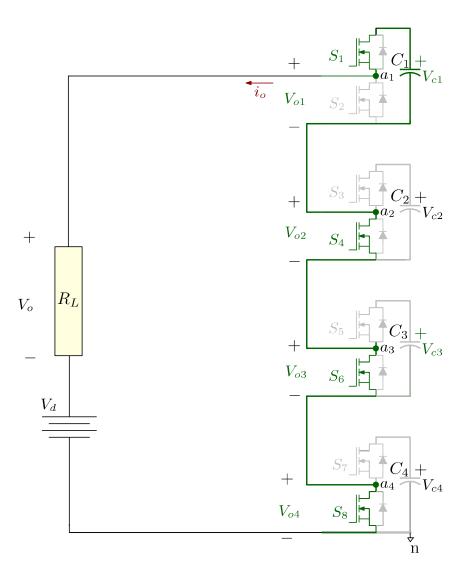

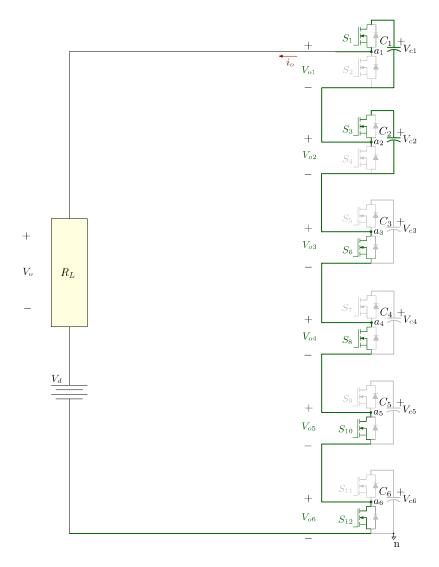

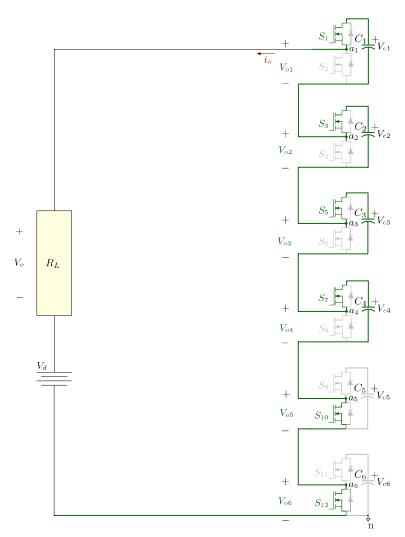

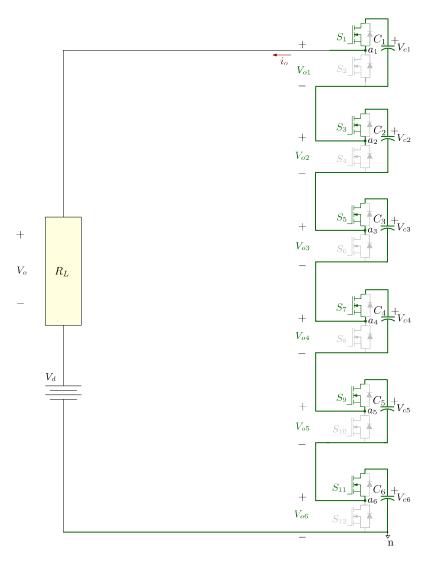

En la Fig. 2.7 se muestra el circuito de un inversor multinivel monofásico tipo H o puente completo, en cada SM hay una configuración HB, se dividen en 2 partes; un brazo superior y un brazo inferior, cada brazo superior e inferior forma una pierna o fase, tiene un inductor buffer conectado en serie con los SMs y por último una carga  $R_oL_o$  conectada en los puntos  $V_{\rm pa}$  y  $V_{\rm pb}$ .

Figura 2.7: Inversor Multinivel Monofásico.

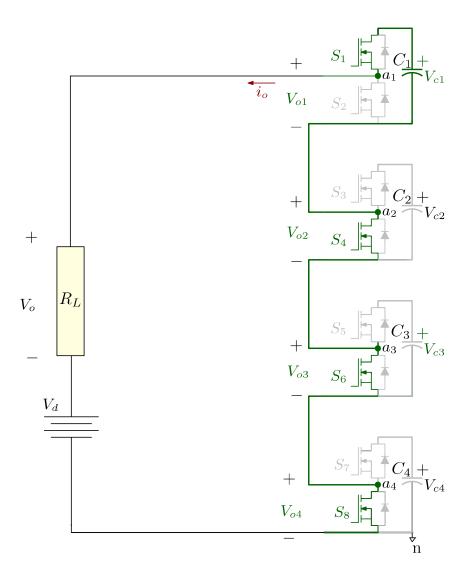

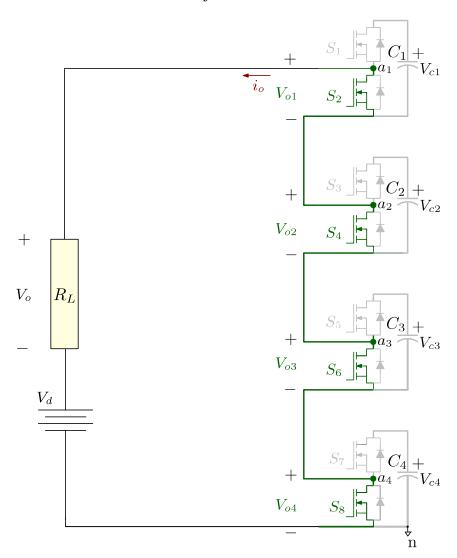

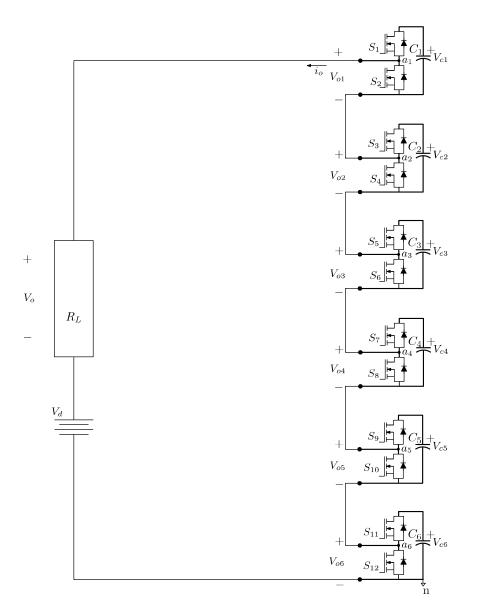

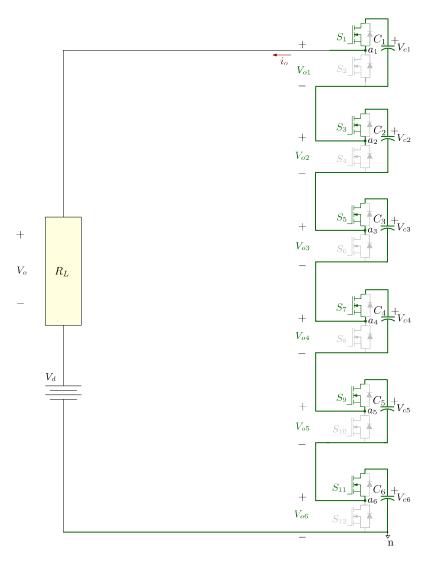

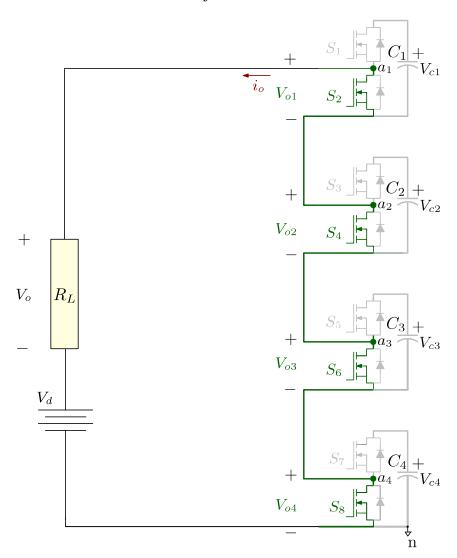

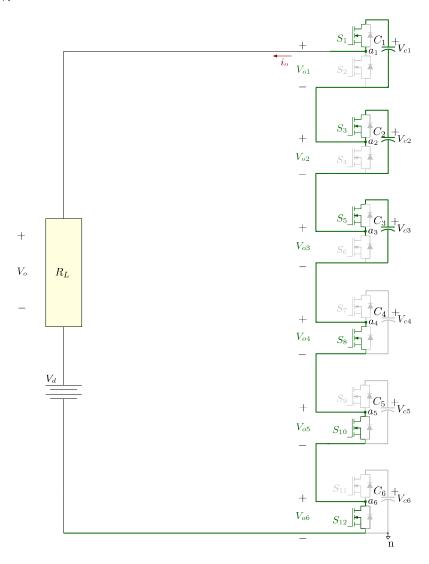

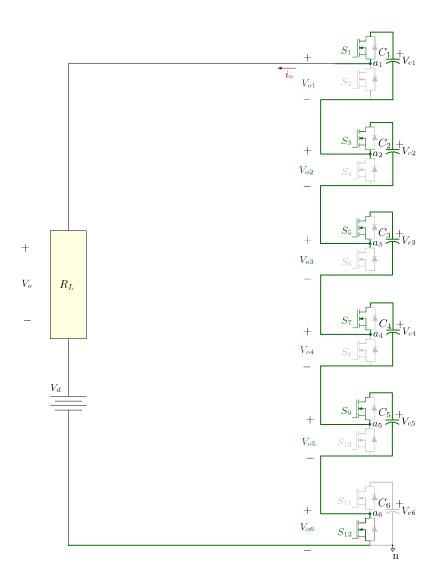

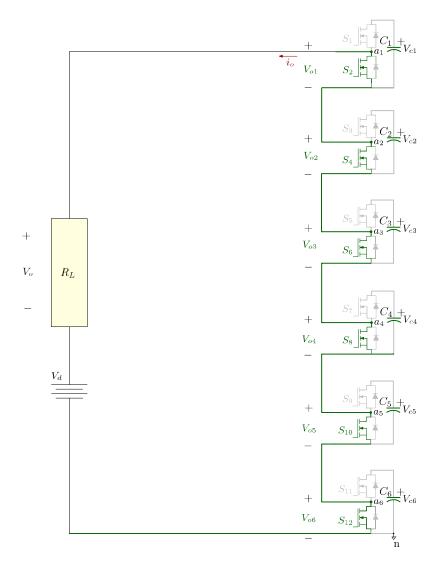

En la Fig. 2.8 se ve la versión trifásica del circuito de un inversor multinivel, como fue explicado en la Fig. 2.7 prácticamente es el mismo principio, sólo se extiende las piernas o fases del circuito, el número de SMs aumentan por fase, ya que, se contará con más transistores, también aumentará el número de capacitores de almacenamiento y por último su carga RL en estrella.

Figura 2.8: Inversor Multinivel Trifásico.

#### 2.9. Conclusiones

En este capítulo se describió una clasificación de los inversores multinivel junto con las topologías que existen en la actualidad, además de una pequeña descripción del inversor multinivel ya que en la actualidad son los más usados de la industria, por ser los más adecuados para aplicaciones de media tensión y alta potencia. Así pues, se explicó la topología MMC propuesta para este trabajo, por ejemplo, se especifica la estructura de las piernas o fase que forman los brazos inferiores y superiores, para que son los inductores buffers. Por otra parte se analizó el principio de operación de un SM, asimismo se realizó el análisis correspondiente al SM, es decir, que en este estudio se obtuvieron los estados de conmutación, por otro lado se explicaron las diferentes técnicas de modulación para controlar al MMC, la técnica de vector espacial es explicada junto a cómo se origina la matriz de  $\alpha-\beta$  y también una breve explicación de dónde se originan esas matrices de Línea y Fase. Y por último, una pequeña explicación de una simulación de un inversor monofásico y trifásico.

Para finalizar, el estado de conmutación del capacitor será cargado o tendrá que ser descargado, esto se logra mediante la dirección de la corriente. Por último, se explicará en el capítulo siguiente la importancia del estado de carga y descarga del capacitor y se hablará del principio de funcionamiento del algoritmo propuesto para esta tesis.

# Capítulo

# Algoritmo para el control de voltajes de los capacitores

En este capítulo se explican algunos algoritmos que existen en la actualidad usados para regular el voltaje en el capacitor de cada capacitor. En primer lugar, estos algoritmos son empleados en los convertidores multinivel ya que solucionan el problema del desbalance de los voltajes de los capacitores por lo que es necesario la implementación de estos algoritmos junto con los algoritmos de ordenamiento. En segundo lugar, se describe el algoritmo propuesto y su principio de funcionamiento en efecto el algoritmo se rige por el principio de operación de un PWM, es decir se compara con una señal de referencia contra una señal portadora el resultado será muchos pulsos que controlaran los transistores pero esto será posible sabiendo el estado del capacitor es decir si estará cargado o no lo está, para poder elegir que capacitor es insertado, cual es el que se va a desacoplar para ser cargado. Por último, se explican simulaciones hechas en Simulink, la simulación de un MMC monofásica y trifásica ambas simulaciones contienen el algoritmo propuesto y se comprueba la teoría de la topología multinivel y se observa cómo va a interactuar el algoritmo.

# 3.1. Algoritmos existentes

En la actualidad hay una gran variedad de algoritmos que se han implementado con buenos resultados, con respecto a estos algoritmos su fortaleza en definitiva arregla el problema del desbalanceo de los voltajes en los capacitores, este es uno de los problemas que presenta la topología MMC, el problema es ocacionado al aumentar los niveles y cuando la frecuencia de conmutación es menor, por lo cual requiere una estrategia de control combinado con una técnica de modulación, cual permite el balanceo y el control de los voltajes para reducir el THD y las pérdidas por conmutación. En [11] se explican detalladamente dos tipos de control para balancear los voltajes de los capacitores, el control promedio que es el más usado y el control balanceado. El algoritmo se basa en la medición de los voltajes de cada capacitor y ordenándolos [12] su algoritmo se basa en medir los voltajes de cada brazo y ordenarlos, después se calculan el número de celdas o SMs en un estado ON o encendidas, para que decida el orden para ser insertado, esto es posible sabiendo polaridad de la corriente. En otro algoritmo mide la corriente del brazo para determinar cuál será insertado o removido, es decir, se toman los SMs con mayor voltaje para ser descargados y para los capacitores que tienen un voltaje menor se cargaran, en pocas palabras se tiene que SM=ON (cargados), SM=OFF (descargados), después se pone en un estado de espera esto es para que la información capturada de toda la medición sea analizada y así selecciona si se insertan o no los SMs, también cuando elige capacitores en modo SM=ON pero con un voltaje menor se mantiene en baipás igualmente para los capacitores con alto voltaje [13] y por último [14] se explica detalladamente su algoritmo usando una adquisición de datos para guardar todas las variables involucradas con eso se compara si el voltaje del SM es mayor que el voltaje promedio de los capacitores del brazo superior o del brazo inferior  $V_{CM} > V_{CP,avg}$  y  $V_{CM} > V_{CNavg}$  y dependiendo la polaridad de la corriente del brazo medido se tendrá uno de estos 3 modos "S=1", "PWM", "S=0" si K=0 se tiene dos modos "S=1" o "PWM" si K=n también se tiene 2 modos "S=0" y "PWM", la variable K es el número de SM que serán insertados o los que no se insertan.

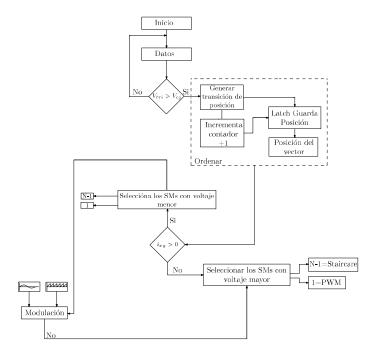

### 3.2. Algoritmo propuesto

El algoritmo propuesto contempla primeramente el ordenamiento de los voltajes de los SMs, según el nivel de voltaje presente en ellos. En la literatura se encuentra una amplia variedad de algoritmos de ordenamiento de los SM; como referencia se puede tomar el algoritmo de la burbuja [15], sin embargo éste es computacionalmente muy demandante por lo que requiere un procesador suficientemente rápido para ejecutar las operaciones en cada periodo de conmutación. Se emplea a la frecuencia del PWM [16], los requerimientos del procesamiento aumentan. Algunas alternativas consisten en conmutar a la frecuencia fundamental, no obstante con mayores exigencias de capacitancia [17]. Algunos algoritmos, como el presentado en [17] pueden prescindir de sensores de corriente.

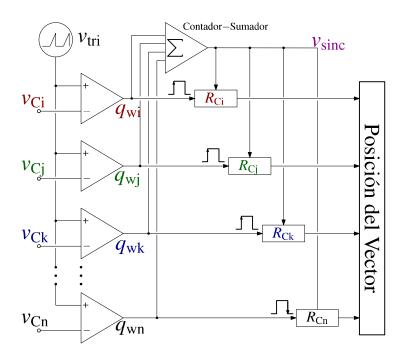

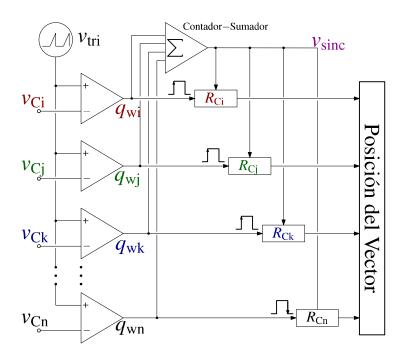

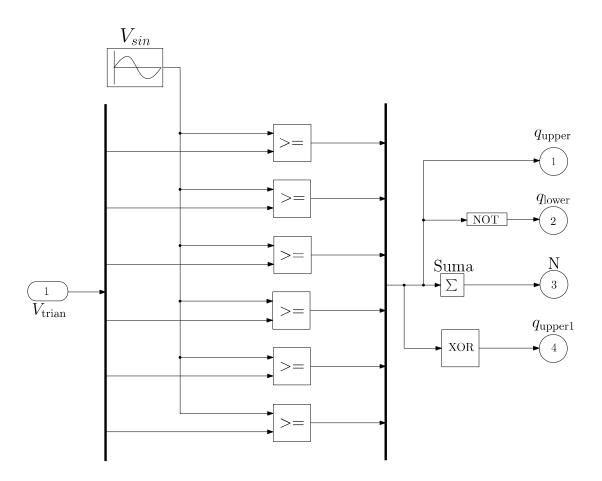

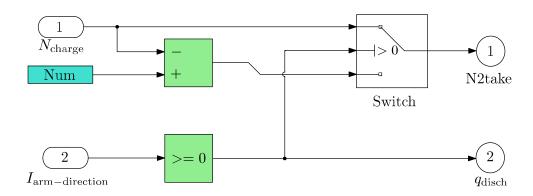

En este trabajo se propone un algoritmo basado en un comparador analógico que genera señales de interrupción adecuadas para aplicarse a un sistema digital. El proceso se puede apreciar en la Figura 3.1, donde existen n comparadores que generan una señal de habilitación  $q_{\text{Cw}}$ , con w=i,j,k,...n de acuerdo con la siguiente regla:

$$q_{wc} = egin{cases} 1 & ext{si} & V_{tri} > V_{Ci} \\ 0 & ext{en caso contrario} \end{cases}$$

La salida del comparador es empleada para controlar el estado del contador-sumador de la Figura 3.1 se encarga de llevar el orden en el que  $v_{\rm tri}$  es igual o mayor a cada uno de los voltajes presentes en los SMs. Inicialmente, todas las salidas  $q_{\rm Cw}$  se encontrarán en estado lógico bajo y, secuencial y ordenadamente, cambiarán los estados de sus comparadores correspondientes. De esta manera, el contador-sumador pasará de cero ( $v_{\rm Cw} < v_{\rm tri}$ ) hasta un valor de n. En cada transición positiva de  $q_{\rm Cw}$ , el valor del contenido actual del contador-sumador es guardado en el registro correspondiente  $R_{\rm Cw}$ . Finalmente, cada registro contendrá la posición ordenada que le corresponda a cada SM, según el voltaje del capacitor medido.

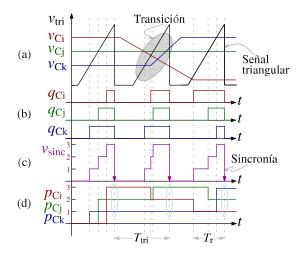

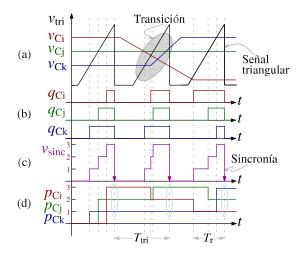

En la Figura 3.2 se muestran las formas de onda más importantes del algoritmo propuesto, en

Figura 3.1: Diagrama de bloques del comparador de niveles de voltaje.

la Figura 3.2 (a) se consideran tres niveles diferentes de voltaje  $v_{\rm ci}, v_{\rm cj}, v_{\rm ck}$ , estos son los voltajes de los capacitores de un SM, con el fin de comparar ese voltaje con una señal triangular, en la Fig. 3.2 (b) son los pulsos ordenados que resultan de la comparación medida, en la Figura 3.2 (c) es la suma de todos los pulsos que llevan el orden de secuencia, y por último en la Figura 3.2 (d) es la posición que ocupa cada SM. La velocidad con la que se ejecuta dicho algoritmo depende de la frecuencia  $F_{\rm tri}=1/T_{\rm tri}$  la cual debe ser seleccionada cuidadosamente en función del esquema de modulación empleado [18].

El tiempo de ejecución del algoritmo, simbolizado como  $T_{\rm r}$  en la Figura 3.2, está relacionado con el número de SMs que son instalados en cada brazo. Adicionalmente, la actualización de los registros ordenados debe coincidir con los cambios de niveles, es decir, estar en sincronía con las conmutaciones de los SMs, con el fin de no incrementar las pérdidas por conmutación.

En las señales de la Figura 3.2 se presenta el peor de los escenarios en el cual una transición ocurre sin ser detectada ya que después de haberse activados los comparadores correspondientes. No obstante, una vez estabilizados los voltajes en los SMs, el índice correspondiente es obtenido

exitosamente. La repercusión de este hecho, no tiene efectos negativos y significativos en la regulación de voltaje y por ende, en el voltaje de salida. En la Figura 3.3 se ve el diagrama de flujo del algoritmo propuesto.

Figura 3.2: Algoritmo de ordenamiento de los SMs según su nivel de voltaje.

Figura 3.3: Diagrama de flujo.

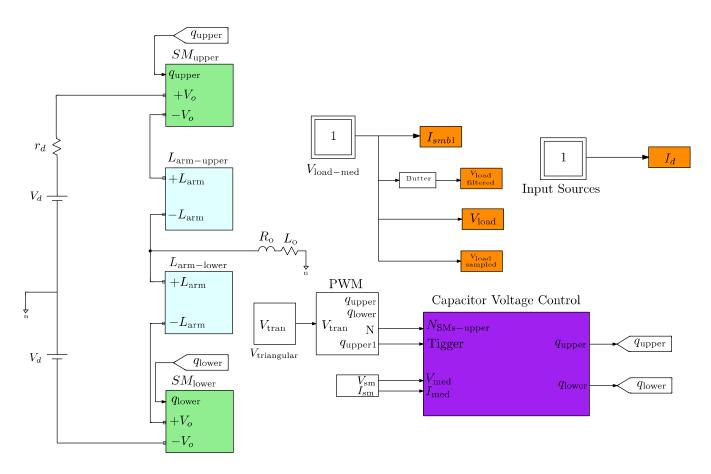

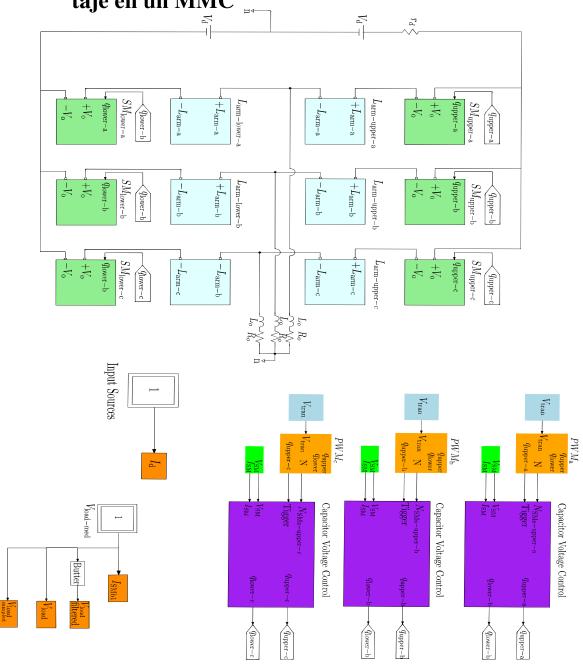

# 3.3. Simulación del algoritmo propuesto

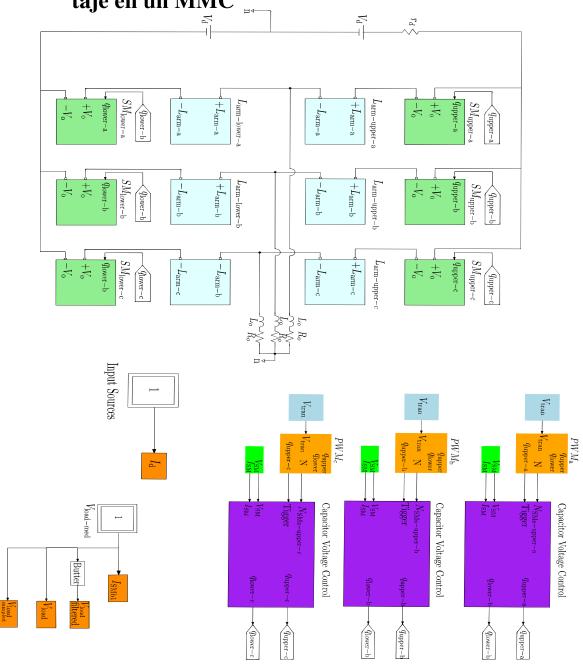

En la Figura 3.4 se observa un diagrama de un MMC Monofásico que es implementado en Simulink, en esta simulación se usarán 6 SMs para cada brazo, también se explicará cómo actúa el algoritmo.

Figura 3.4: Circuito de un MMC de una fase hecho en Simulink.

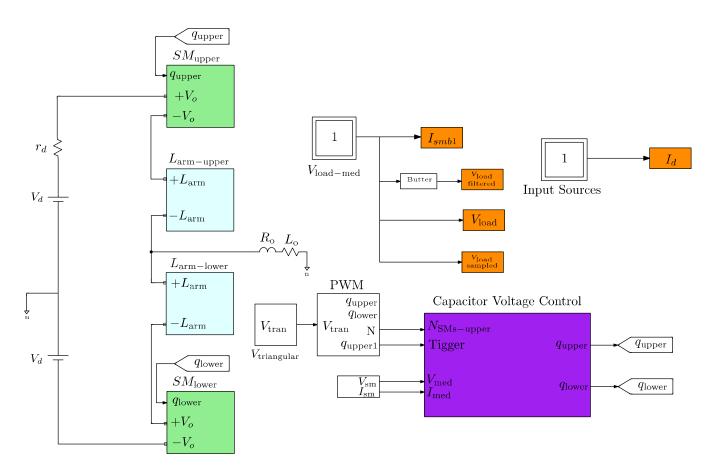

#### 3.3.1. Simulación de una fase o pierna

En la Figura 3.5 se ve un inversor monofásico con configuración de medio puente, conformado por una fase o pierna, se conforma por dos brazos, un brazo superior y un brazo inferior, todos los SMs están dentro de los bloques  $SM_{\rm upper}$  y  $SM_{\rm lower}$ , dentro de cada bloque se encuentran todos los SMs, cada SM tiene una configuración de medio puente (HB) y un capacitor de

almacenamiento, en los bloques  $L_{\rm arm-upper}$  y  $L_{\rm arm-lower}$  se encuentran el inductor buffer que su principal función es limitar las corrientes circulantes provocadas por la diferencia de voltaje de todas las fuentes del circuito. Estos 2 bloques están conectados en cascada así forman el brazo superior y brazo inferior, todo eso se conecta a una fuente de c.d. y por último tiene una carga RL conectada entre los 2 brazos.

Figura 3.5: Simulación de medio puente.

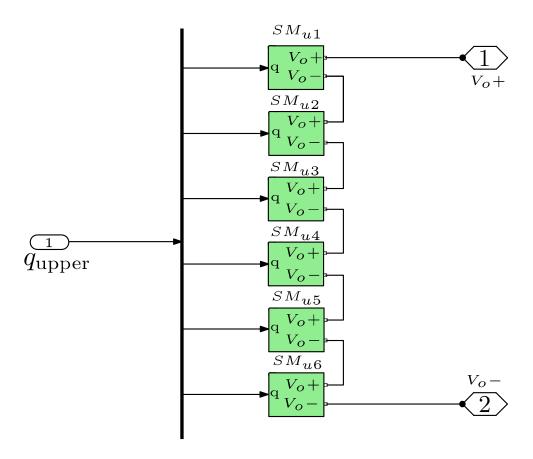

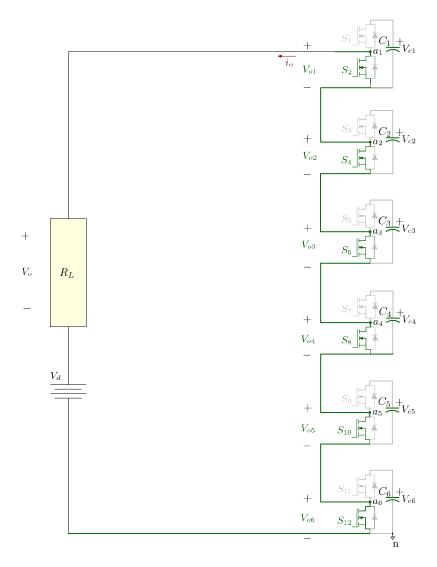

#### 3.3.2. Simulación de un brazo

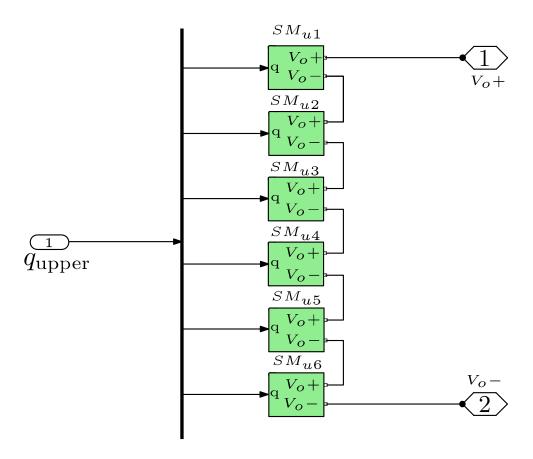

En la Figura 3.6 se muestran todos los SMs de un brazo, cada SM contiene dos transistores en serie con un capacitor en paralelo, en este caso se muestra el brazo superior pero también el brazo inferior tiene los mismos SMs, en total son 12 SMs, 6 SMs para cada brazo, todos los SMs están conectados en cascadas y conectados a un bus, en ese bus llegan un conjunto de pulsos para controlar cada submodulo.

Figura 3.6: Brazo superior.

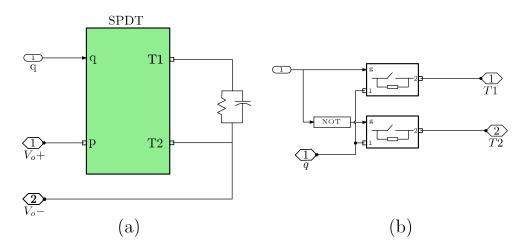

#### 3.3.3. Bloque del SM en Simulink

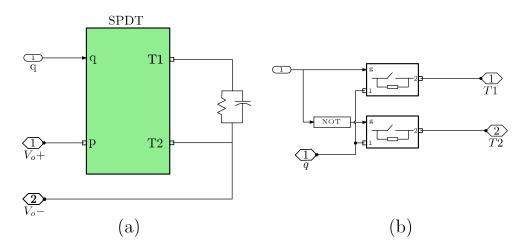

En la Figura 3.7 (a) se muestra el SM que fue hecho en simulink este tiene conectado en paralelo un capacitor de almacenamiento y su resistencia parásita en la Figura 3.7 (b) se muestra lo que tiene internamente el SM.

**Figura 3.7:** Interior de un SM hecho en Simulink: a) SPDT y b) Transistores.

#### 3.3.4. Bloques de señales en el Simulink

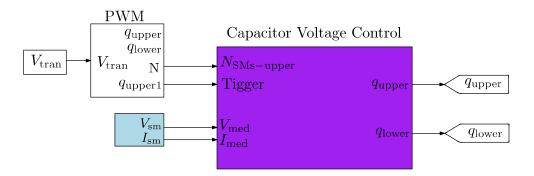

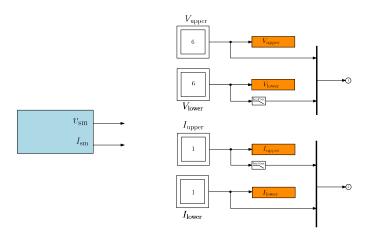

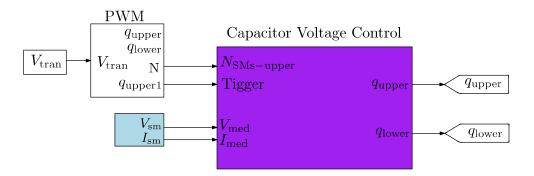

En la Figura 3.8 se muestran 4 bloques, a la izquierda está los bloques de señal, el primer bloque es la señal triangular  $V_{\rm trian}$  que se conecta al bloque que genera el PWM, su principal función es generar una señal cuadrada, el cuadro de color azul su principal función es medir el voltaje de cada SM y la corriente total de cada brazo y por último se mandan al bloque de color morado que es el algoritmo, en ese bloque se encuentra el algoritmo propuesto del proyecto. En la Figura 3.14 se explicará cómo se conforma y se explicará su funcionamiento.

**Figura 3.8:** Señal  $V_{tri}$ , Señal PWM, algoritmo propuesto y Medición de voltaje y corriente.

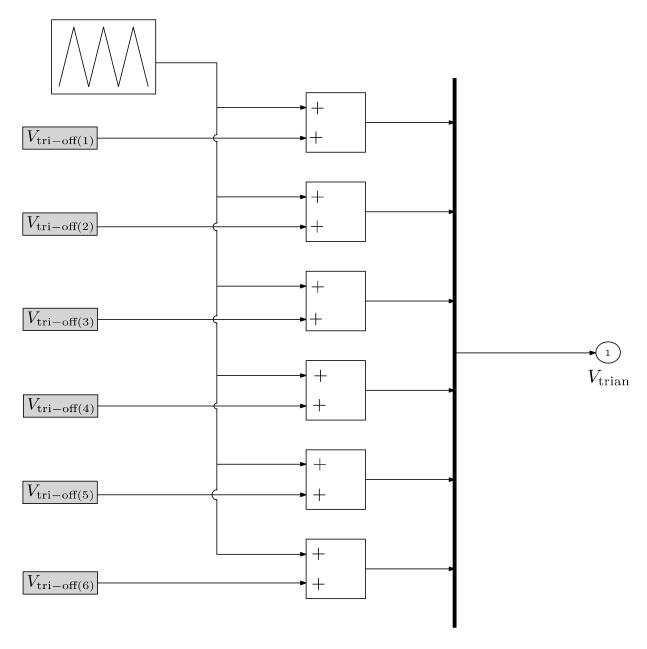

#### 3.3.5. Señal de voltaje triangular

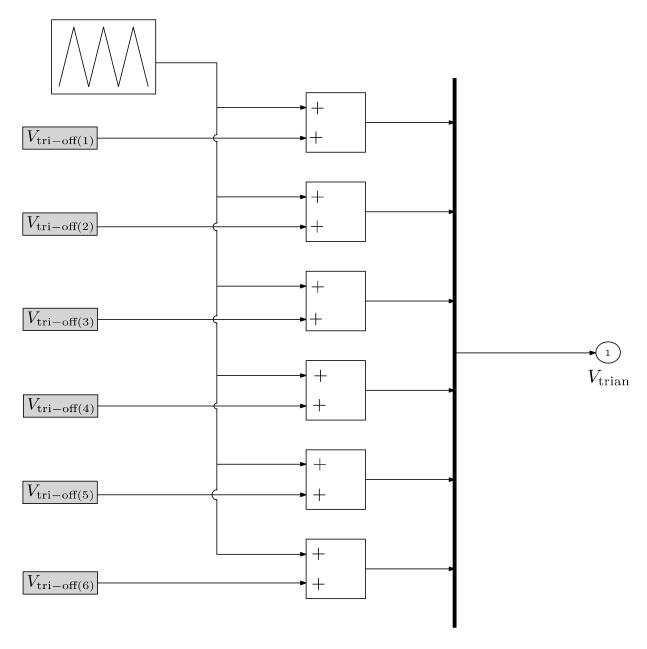

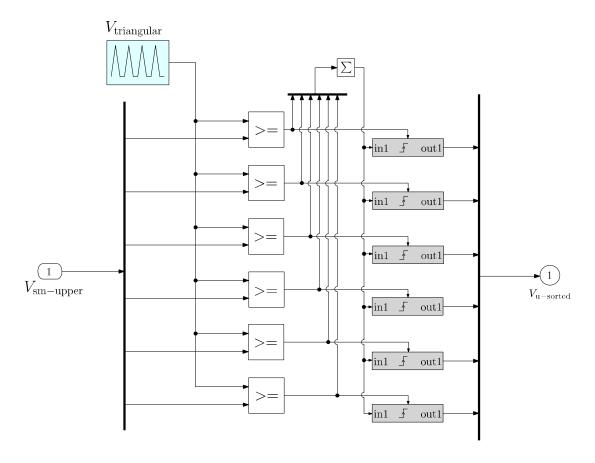

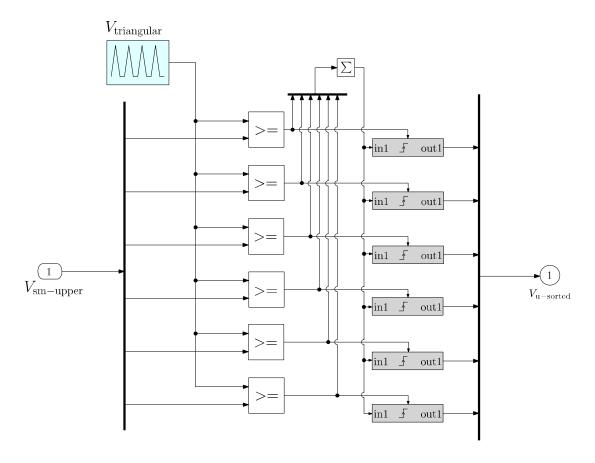

En la Figura 3.9 se observa el esquema de cómo se generan la señal triangular para ser usada en el bloque del PWM, se generan 6 señales constantes que se comparan contra una señal triangular o señal portadora, al final todas las señales entrarán a un bus para después ser mandadas al bloque PWM.

Figura 3.9: Señal de voltaje triangular.

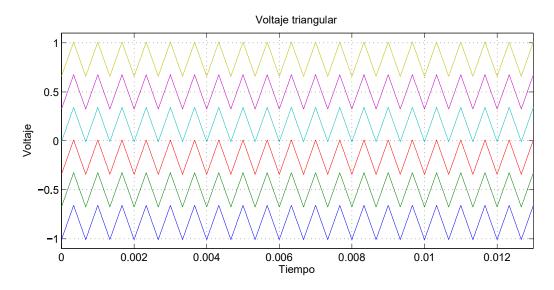

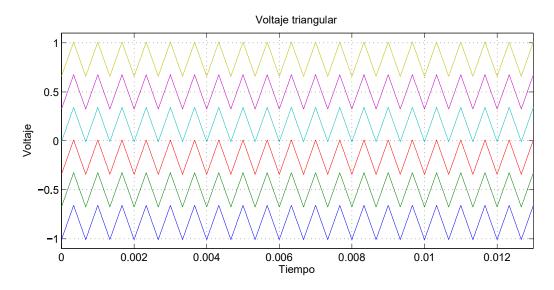

En la Figura 3.10 se muestran las señales obtenidas después de la comparación, el valor de la frecuencia  $F_{\rm tri}$  es de 3kHz , son 6 señales portadoras para todos los SM del brazo superior, también hay señales para el brazo inferior.

Figura 3.10: Señales triangulares.

En la Tabla 3.1 se muestran los valores promedios, el valor de todas las señales que se generan en el  $V_{\rm tri}$ .

Tabla 3.1: Tabla de los valores de  $V_{\rm tri}$  .

| Señales $V_{ m tri}$  | Valor   |  |  |  |  |

|-----------------------|---------|--|--|--|--|

| $V_{ m tri\_off}(1)$  | -0.8333 |  |  |  |  |

| $V_{\rm tri\_off}(2)$ | -0.5    |  |  |  |  |

| $V_{\rm tri\_off}(3)$ | -0.1666 |  |  |  |  |

| $V_{ m tri\_off}(4)$  | 0.1666  |  |  |  |  |

| $V_{\rm tri\_off}(5)$ | 0.5     |  |  |  |  |

| $V_{\rm tri\_off}(6)$ | 0.8333  |  |  |  |  |

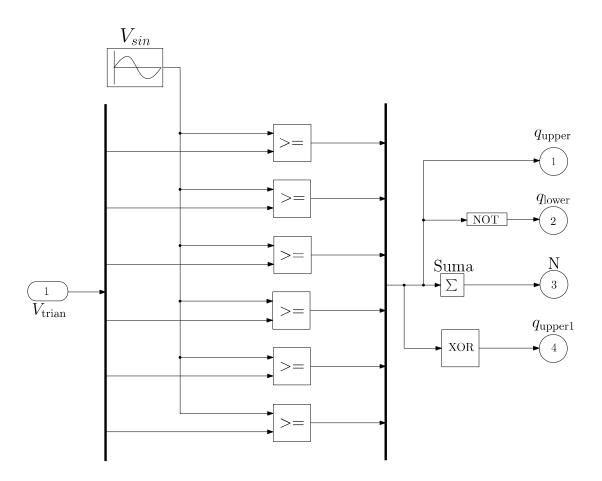

#### 3.3.6. Modulación de ancho de pulso (PWM)

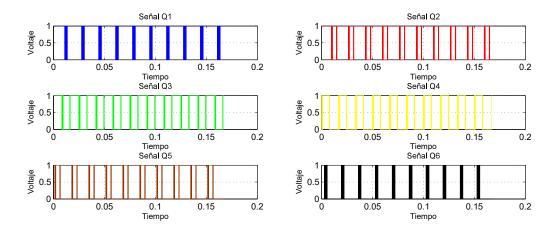

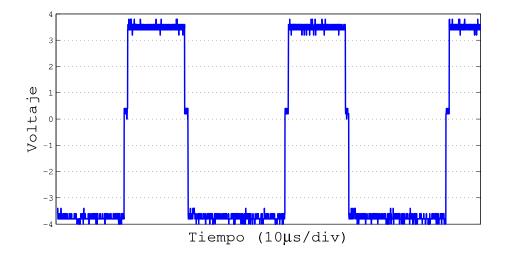

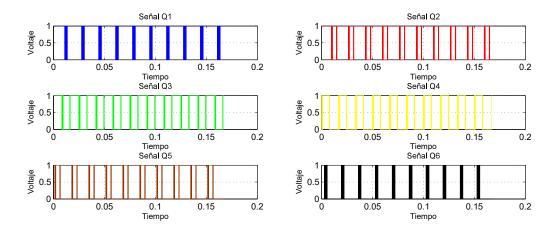

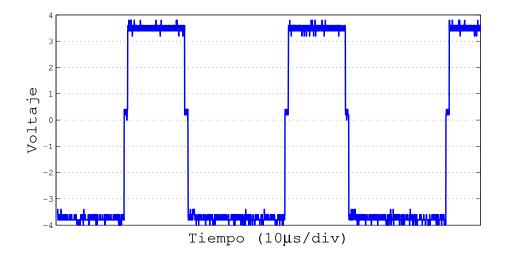

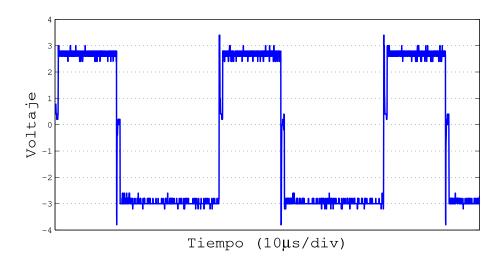

En la Figura 3.11 se muestra la implementación de la técnica de Modulación de Ancho de Pulso (PWM), una señal triangular o señal portadora se compara contra una señal senoidal o señal de referencia. Las señales de disparo para el control de los SMs del inversor se ven en la Figura 3.12.

Figura 3.11: Generación del PWM.

Es una señal de dispara para el control de cada SM, ya que controla el encendido o apagado de cada celda, en pocas palabras cada transistor se lleva a la región de saturación o de corte.

Figura 3.12: Señales de disparo.

#### 3.3.7. Bloque Measurements

En la Figura 3.13 se ve un bloque, el cual mide dos variables muy importantes para el funcionamiento óptimo del algoritmo, las variables son: el voltaje de cada SM y la corriente de cada brazo, ya que es necesario la medición de estas dos variables para el algoritmo. Porque con el voltaje medido, el algoritmo podrá comparar ese voltaje con una señal portadora, es decir, el algoritmo tiene el principio de un PWM. Por último, se mide la corriente de cada brazo del inversor para saber la dirección de la corriente. En el apartado 3.3.8 se explicará a detalle porqué es de suma importancia la medición de estas dos variables.

Figura 3.13: Bloque de medición voltaje y corriente.

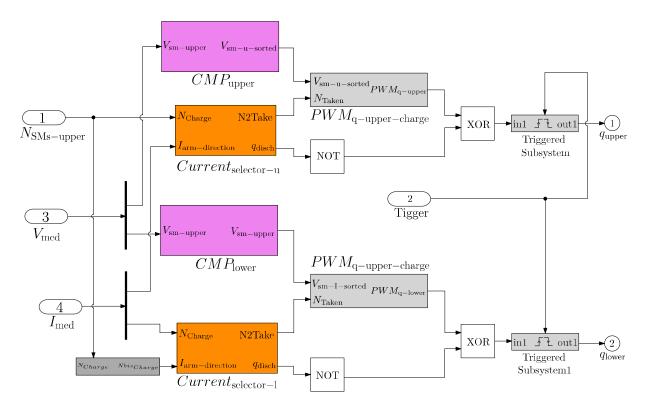

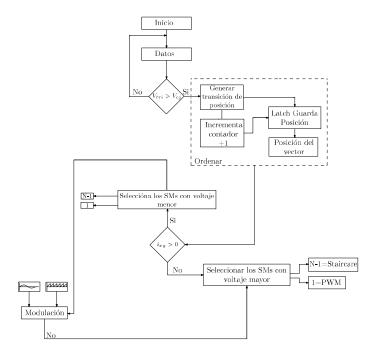

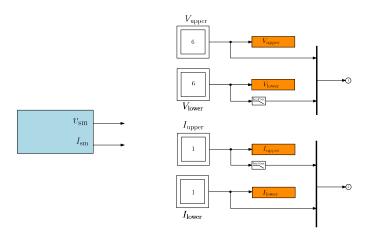

#### 3.3.8. Módulo interno del algoritmo

En la Figura 3.14 se muestra cómo está compuesto internamente el algoritmo, se observan diferentes bloques: los bloques  $CMP_{\rm upper}$  y  $CMP_{\rm lower}$ , en su interior se encuentra una parte del algoritmo ya que en estos dos bloques su función principal es ordenar los voltajes de los capacitores, es decir, contienen la posicion de cada capacitor, uno para el brazo superior y otro para el brazo inferior, los bloques  $Current_{\rm selector-u}$  y  $Current_{\rm selector-l}$  también existe para cada brazo, este bloque mide la corriente para saber su polaridad, los bloques  $PWM_{\rm q-upper-charge}$  y  $PWM_{\rm q-lower-charge}$  tienen como principal función saber cuál capacitor estará más cargado o cuál estará menos cargado y por último el bloque de sincronización es una compuerta lógica XOR es el encargado de elegir el capacitor que será insertado, en pocas palabras, cuál está cargado y cuál está descargado y el último bloque es un registro. Este algoritmo se ejecuta para el brazo superior y el brazo inferior, en una versión trifásica se puede usar el algoritmo para cada pierna y cada brazo.

**Figura 3.14:** Algoritmo Propuesto o Control Balanceado.

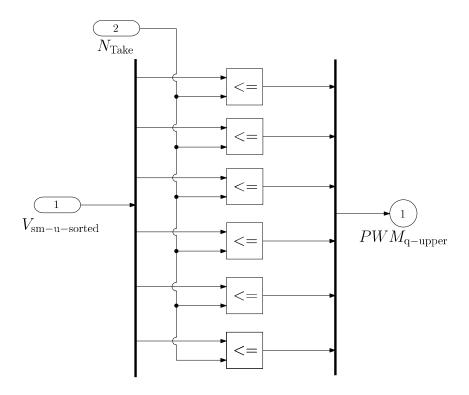

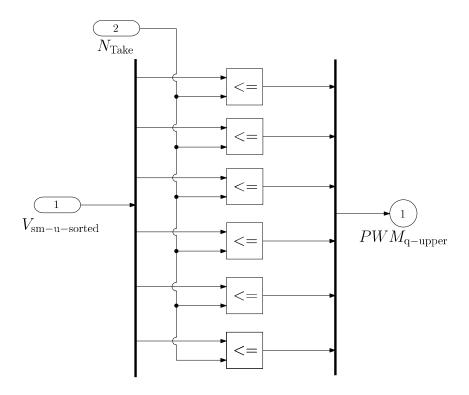

#### 3.3.9. Algoritmo Propuesto bloque de Ordenamiento

En la Figura 3.15 se muestra la primera parte del algoritmo. Esta parte ordena todos los voltajes  $V_{\rm sm-upper}$  este es el voltaje de todos los capacitores del brazo superior, estos voltajes serán las señales de referencia y la otra será la señal triangular o señal portadora  $V_{\rm trian}$ . Entonces la señal de referencia será comparada contra una señal portadora triangular, luego de la comparación se guardan en un registro y por último se ordena por la posición del vector que el capacitor tenga y así decidir cuál tiene más prioridad para ser usado. También para el brazo inferior se acopla un bloque con este principio de operación.

Figura 3.15: Algoritmo de Control Balanceado propuesto.

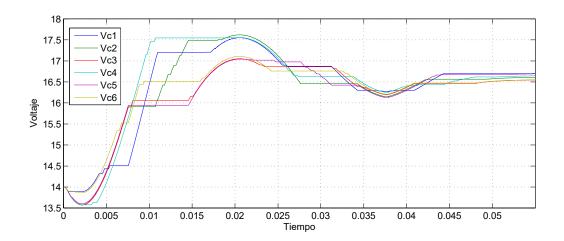

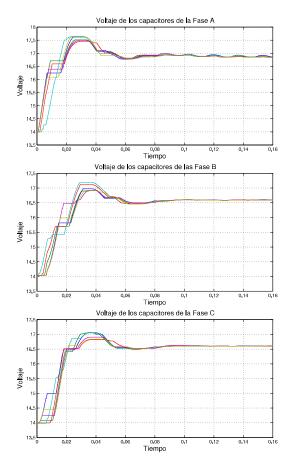

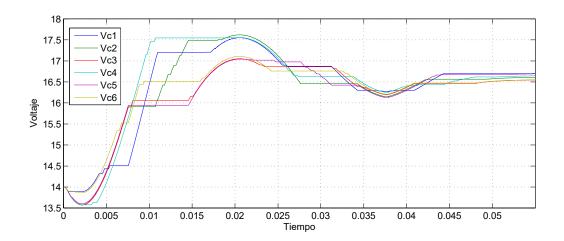

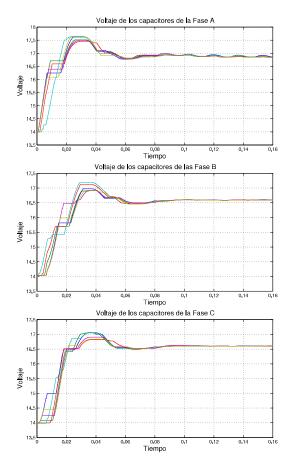

En la Figura 3.16 se ve una gráfica de cada uno de los voltajes de cada capacitor, se observa que todos los voltajes de los capacitores tienen un voltaje inicial de 14 V, la simulación cuenta con 6 voltajes que representan los voltajes de los capacitores, dicha simulación sólo dura 50 ms

y claramente se ve cuando todos los voltajes convergen a 16.7 V, en pocas palabras es el set point, por último, a partir de 45 ms se empiezan a balancear todos los voltajes.

Figura 3.16: Gráfica de los voltajes de los capacitores.

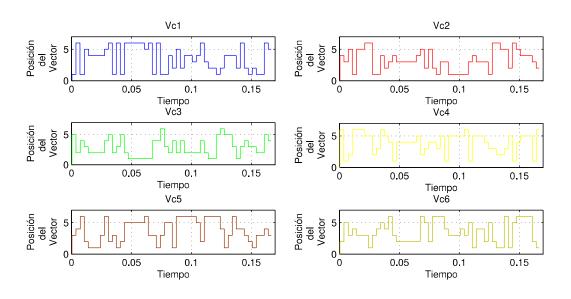

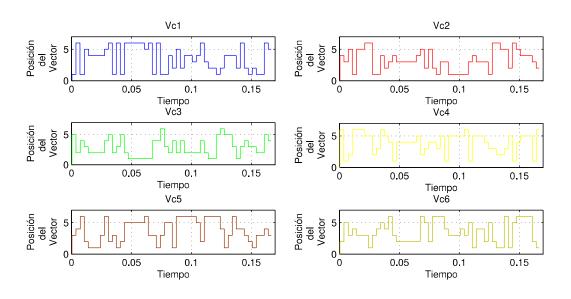

En la Figura 3.17 se observa cuando el algoritmo está trabajando, en todas las gráficas se observan la posición vectorial que ocupa cada capacitor, se representan individualmente para ser mejor apreciado.

Figura 3.17: Gráfica de la posición vectorial de cada capacitor.

#### 3.3.10. Medición de la corriente

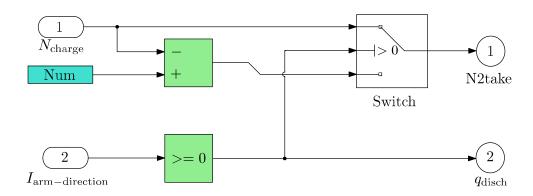

En la Figura 3.18 se muestra lo que contiene internamente en los bloques  $\operatorname{Current}_{\operatorname{selector-u}}$  y  $\operatorname{Current}_{\operatorname{selector-l}}$ , su principal función es medir la dirección del flujo de corriente que circula por todo el brazo, es decir que puede ser el brazo superior o el brazo inferior, si la corriente i>0 significa que los capacitores se encuentran descargados y serán cargados, así que el SM será desacoplado para que el capacitor tenga tiempo de poder cargarse y si la corriente i<0 esto quiere decir que el capacitor está cargado en pocas palabras se va a insertar para ser descargado.

Figura 3.18: Medición de la corriente.

#### 3.3.11. Voltaje de los capacitores balanceados en el brazo superior

En la Figura 3.19 se muestra lo que tiene internamente los bloquea  $PWM_{q-upper-charge}$  y  $PWM_{q-lower-charge}$  de la Figura 3.14, su principal función es comparar la señal de la corriente  $N_{\rm take}$  contra la señal de los voltajes de los capacitores  $V_{\rm sm-u-sorted}$  el resultado es la selección de los capacitores para ser insertados para su descarga o el desacoplo de los capacitores que no están cargados, y para finalizar después de la comparación se mandan pulsos hacia la compuerta XOR.

**Figura 3.19:** Comparador de la posición vectorial de los capacitores contra la corriente total del arm-Upper.

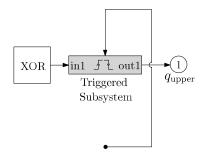

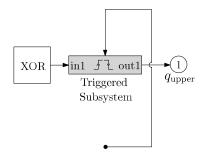

# 3.4. XOR y sincronización

Por último, en la Figura 3.20 se explicará la importancia del bloque XOR, como ya antes en la Figura 3.14 se explicó, su función principal es elegir qué capacitor serán los que se insertan o cuáles son los que no se van a insertar. Con la Tabla 3.2 se explicará el funcionamiento de un XOR, y por último el bloque Triggered es un registro para guardar la posición del vector del algoritmo y después se va al brazo superior o brazo inferior a controlar los transistores.

Figura 3.20: Principio del XOR.

En la Figura 3.21 se observa el símbolo de una puerta lógica XOR y su tabla de la verdad se muestra en la Tabla 3.2, para poder entender el funcionamiento de la Fig. 3.20 se explicará los principios básicos de esta puerta lógica.

$$A \longrightarrow S$$

**Figura 3.21:** *XOR*

En la Tabla 3.2 se ve la tabla de la verdad de la puerta lógica XOR, se tiene dos entradas y una salida, una de las entradas es A y la otra entrada es B, por último S es la salida del sistema, el valor de A y B es 0 un nivel bajo o 1 un nivel alto, es decir falso o verdadero, si una de las dos entradas A o B es verdadera en la salida sería verdadero en pocas palabras 1 pero si ambas entradas son falsas o verdaderas en la salida como resultado será falso en pocas palabras 0, en pocas palabras si las dos entradas resultan ser iguales es decir verdaderas o falsas la salida resulta ser falsa pero si en las entradas no son iguales con esto quiero decir que son diferentes su salida será verdadera. Las expresiones algebraicas de la puerta XOR es  $\bar{A} \oplus B = A \oplus \bar{B}$ .

**Tabla 3.2:** Tabla de la verdad de la compuerta XOR.

| A | В | $A \oplus B$ |

|---|---|--------------|

| 0 | 0 | 0            |

| 0 | 1 | 1            |

| 1 | 0 | 1            |

| 1 | 1 | 0            |

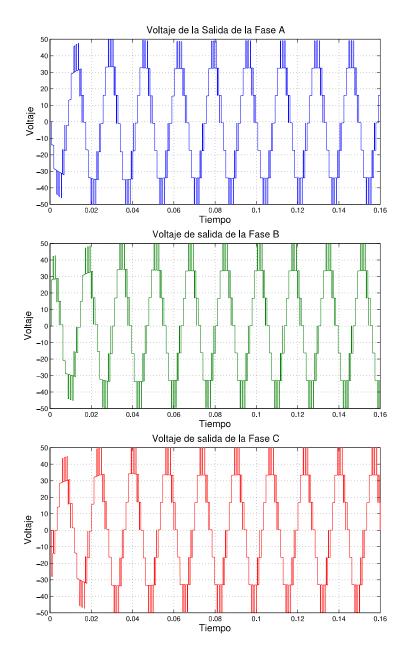

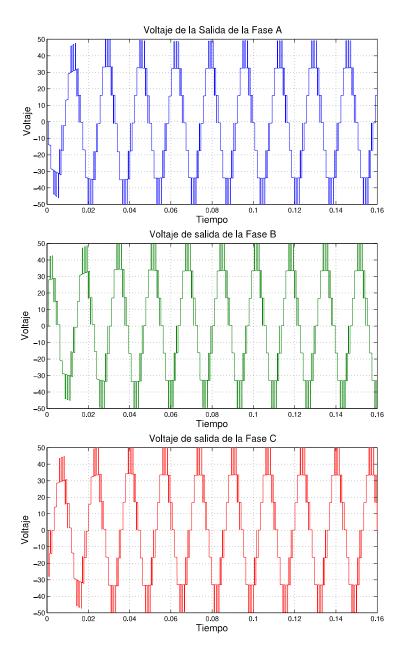

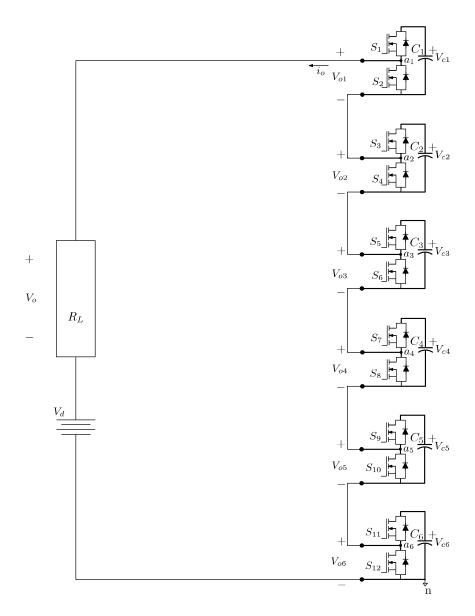

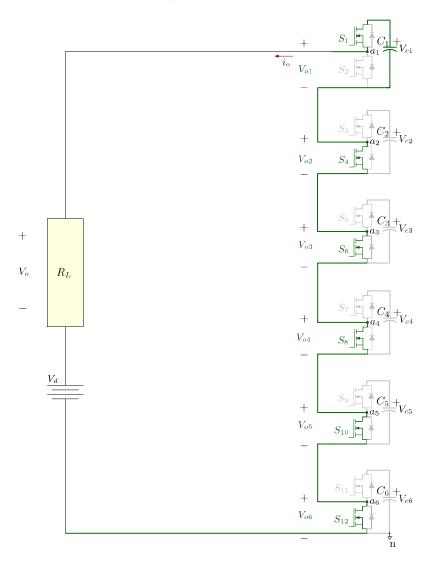

# 3.5. Simulación trifásica del algoritmo de regulación de voltaje en un MMC

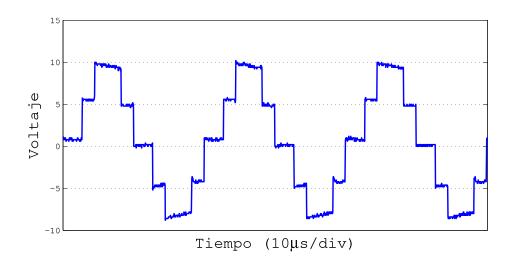

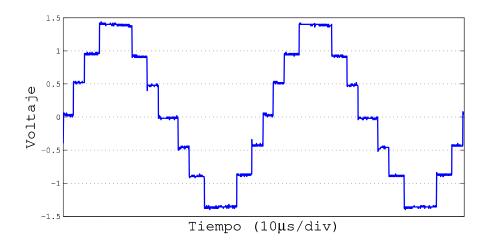

Figura 3.22: Inversor Multinivel Trifásico.