# INSTITUTO TECNOLÓGICO SUPERIOR DE IRAPUATO

# ESTUDIOS CON RECONOCIMIENTOS DE VALIDEZ OFICIAL NÚMERO 11-00065

# SISTEMA DE RECTIFICACIÓN CON UNA ETAPA DE CONVERTIDOR CD-CD

OPCIÓN I: TESIS PROFESIONAL

# QUE PARA OBTENER EL GRADO DE: MAESTRO EN INGENIERÍA

#### PRESENTA:

CHRISTOPHER JESÚS RODRÍGUEZ CORTÉS

DIRECTORES DE TESIS: DR. JOSÉ MIGUEL SOSA ZÚÑIGA DR. MARIO ALBERTO JUÁREZ BALDERAS

Instituto Tecnológico Superior de Irapuato

Dirección General

Irapuato, Guanajuato, <mark>07/julio/2022</mark> MEMORÁNDUM No. CIPI-004/2022 ASUNTO: Autorización de impresión de tesis de maestría

### DR. GERARDO VÁZQUEZ GUZMÁN PRESIDENTE DEL CONSEJO DE POSGRADO MAESTRÍA EN INGENIERÍA ELECTRÓNICA PRESENTE

Por medio de la presente y a solicitud del comité tutorial integrado por:

Dr. José Miguel Sosa Zúñiga

Dr. Mario Alberto Juárez Balderas

Dr. Adolfo Rafael López Núñez

Dr. Gilberto Muñoz Moreno

se autoriza la impresión de la tesis titulada "Sistema de rectificación con una etapa de convertidor CD-CD" realizada por el estudiante C. Christopher Jesus Rodriguez Cortes con número de control IP20110060 la cual ha sido desarrollada dentro del programa de la Maestría en Ingeniería Electrónica bajo la dirección del Dr. José Miguel Sosa Zúñiga y la codirección del Dr. Mario Alberto Juárez Balderas y ha sido revisada y aprobada por el comité tutorial antes mencionado.

Sin otro en particular, le envío un cordial saludo.

ATENTAMENTE

Excelencia en Educación Tecnológica Espíritu de Excelencia en Desarrollo Tecnológico

NSTITUTO TECNOLÓGICO SUPERIOR

DE IRAPUATO

M. I. OSCAR OMAR CUIN MACEDO

TITULAR DE LA DIRECCIÓN ACADÉMICA PRESIDENTE DEL CIPI

TECNM/ITS DE IRAPUATO

ccp. M. I. J. Sacramento Solórzano Lujano M.C. Akira Torreblanca Ponce Archivo Titular de la Coordinación de Ingeniería Electrónica Titular del Departamento de Investigación para su conocimiento y atención mismo fin

Carr. Irapuato-Silao km 12.5 Colonia El Copal, Irapuato, Guanajuato, C.P. 36821

Tels. 4626967900 y 4626067602, tecnm.mx | irapuato.tecnm.mx

# Constancia de aprobación de la tesis

La tesis Sistemas de rectificación con una etapa de convertidor CD-CD presentada para obtener el Grado de Maestro en Ingeniería Electrónica fue elaborada por el Ing. Christopher Jesús Rodriguez Cortes y aprobada el 07 de julio de 2022 por los suscritos, designados por el Consejo de Posgrado de la Maestría en Ingeniería Electrónica del Tecnológico Nacional de México / Instituto Tecnológico Superior de Irapuato.

Dr. José Miguel Sosa Zúñiga

(Director de la tesis)

Dr. Mario Alberto Juárez Balderas (Director de la tesis)

Dr. Adolfo Rafael López Núñez (Sinodal)

Dr. Gilberto Muñoz Moreno (Sinodal)

# Créditos Institucionales

Esta tesis fue elaborada en el Laboratorio de Eléctrica y Electrónica de Potencia (LEEP) del Tecnológico Nacional de México / Instituto Tecnológico Superior de Irapuato, bajo la dirección de los profesores Dr. José Miguel Sosa Zúñiga y Dr. Mario Alberto Juárez Balderas.

#### **AGRADECIMIENTOS**

Agradezco al Consejo Nacional de Ciencia y Tecnología (CONACYT) mediante la beca para estudios de posgrado, durante el transcurso de la maestría, ya que gracias a esto fue posible realizarla.

Al Instituto Tecnológico Superior de Irapuato (ITESI) por prestar sus instalaciones y equipo, y al Consejo de Posgrado de la Maestría en Ingeniería Electrónica por brindar la oportunidad de pertenecer al posgrado.

A mi asesor Dr. José Miguel Sosa Zúñiga por compartir sus conocimientos y orientación durante el desarrollo de este trabajo de tesis, por su tiempo compartido y consejos que me brindó para culminar la elaboración de esta tesis. Además le agradezco por involucrarme en proyectos de investigación y desarrollar en mi la curiosidad de la investigación. A mi co-asesor Dr. Mario Alberto Juárez Balderas por su apoyo y orientación durante el desarrollo de esta tesis.

Al cuerpo académico de la Maestría en Ingeniería Electrónica, Dr. Adolfo Rafael López Núñez, Dr. Gerardo Vázquez Guzmán, Dr. Gilberto Muñoz Moreno y M.C José Juan Alfaro Rodríguez por su orientación y manera de trabajar para la formación de profesionales.

Al M.I. J. Sacramento Solórzano Lujano por ser la primera persona que confió en mí, por siempre apoyarme y orientarme durante mi formación profesional. Además, le agradezco por involucrarme en diferentes actividades que me permitieron desarrollarme como una mejor persona tanto, en lo profesional como en lo personal y por brindarme su amistad.

Especialmente a mis padres, familia y amigos quienes desde el primer día apoyaron en la decisión de aspirar a la maestría, y durante el transcurso dieron todo su apoyo.

Christopher Jesús Rodríguez Cortés, Irapuato, Guanajuato, México, Julio, 2022.

# NOTACIÓN

# Acrónimos frecuentes

| CA    | Corriente Alterna                                            |

|-------|--------------------------------------------------------------|

| CD    | Corriente Directa                                            |

| CA-CD | Convertidor de Corriente Alterna a Corriente Directa         |

| CD-CD | Convertidor de Corriente Directa a Corriente Directa         |

| EMI   | Electromagnetic Interference (Interferencia electromagnética |

| FP    | Factor de Potencia                                           |

| LCD   | Arreglo de Inductor-Capacitores-Diodos                       |

| MCC   | Modo de Conducción Continua                                  |

| MCD   | Modo de Conducción Discontinua                               |

| PFC   | Power Factor Correction (Corrección del Factor de Potencia)  |

| PI    | Proportional-Integrative (Proporcional-Integral)             |

| THD   | Total Harmonic Distortion (Distorsión Armónica Total)        |

|       |                                                              |

#### RESUMEN

En este trabajo de tesis se presenta el diseño, análisis, simulaciones numéricas, implementación y pruebas experimentales de dos distintos convertidores CA-CD enfocados la mejora del factor de potencia.

La estructura de los convertidores está basada en un rectificador no controlado seguido de un convertidor CD-CD no aislado. Uno de los convertidores incorpora un convertidor reductor multifase que tiene un filtro LC a la entrada. Otro de los convertidores incorpora un convertidor reductor con una relación de conversión extendida.

Ambos convertidores de CD-CD tienen como principales características la reducción del voltaje de entrada y la existencia de un inductor a la entrada del convertidor. Este inductor de entrada permite filtrar las componentes de conmutación hacia la red eléctrica.

Se propone en este trabajo de tesis que los convertidores CD-CD operen en modo de conducción discontinua en la etapa de la salida y en modo de conducción continua el inductor de entrada. Se proponen dos controladores para las dos topologías propuestas que están formados por dos lazos de control; uno de voltaje y uno de corriente. Los controladores propuestos permiten regular el voltaje de salida y hacer seguimiento de la corriente de red, para asegurar un factor de potencia cercano a la unidad. Se implementan dos prototipos experimentales con el objetivo de validar experimentalmente las soluciones propuestos. Los resultados experimentales muestran un desempeño aceptable en lazo cerrado usando los controladores propuestos.

#### ABSTRACT

In this thesis work, the design, analysis, numerical simulations, implementation and experimental tests of two different AC-DC converters focused on improving the power factor are presented.

The structure of the converters is based on an uncontrolled diode rectifier followed by a non-isolated DC-DC converter. One of the converters incorporates a multiphase buck converter that has an LC filter at the input. Another of the converters incorporates a step-down converter with an extended conversion ratio.

The main characteristics of both DC-DC converters are the reduction of the input voltage and the existence of an inductor at the input of the converter that allows the switching components to be filtered towards the electrical grid. In this thesis work, it is proposed that DC-DC converters operate in discontinuous conduction mode in the output stage and in continuous conduction mode in the input inductor. Two controllers are proposed for the two proposed topologies that are formed by two control loops; one for voltage and one for current. The proposed controllers allow the regulation of the output voltage and the tracking of the grid current, to ensure a power factor close to unity. Two experimental prototypes are implemented in order to validate the proposed solutions. The experimental results show an acceptable performance in closed loop using the proposed controllers.

# ${\rm \acute{I}ndice}$

| 1. | Intr | oducci  | ón                                                                  | 15 |

|----|------|---------|---------------------------------------------------------------------|----|

| 2. | Cap  | ítulo I | : Generalidades del proyecto                                        | 17 |

|    | 2.1. | Plante  | amiento del problema                                                | 18 |

|    | 2.2. | Justifi | cación                                                              | 18 |

|    | 2.3. | Objeti  | vo general y objetivos específicos                                  | 19 |

| 3. | Cap  | ítulo I | I: Estado del arte                                                  | 20 |

|    | 3.1. | Métod   | os para la corrección del factor de potencia                        | 2  |

|    | 3.2. | Métod   | os pasivos para la corrección del factor de potencia                | 2  |

|    | 3.3. | Métod   | os activos para la corrección del factor de potencia                | 23 |

|    |      | 3.3.1.  | Convertidores operados en Modo de Conducción Continua               | 24 |

|    |      | 3.3.2.  | Convertidores operados en Modo de Conducción Discontinua            | 26 |

|    |      | 3.3.3.  | Análisis comparativo de convertidores CA-CD operados en Modo de     |    |

|    |      |         | Conducción Discontinua                                              | 3  |

| 4. | Cap  | ítulo I | III: Marco teórico                                                  | 35 |

|    | 4.1. | Calida  | d de la energía                                                     | 36 |

|    | 4.2. | Norma   | ativas relacionadas con la calidad de la energía                    | 3  |

| 5. | Cap  | ítulo I | V: Sistemas de rectificación con una etapa de convertidor CD-       |    |

|    | CD   | •       |                                                                     | 4  |

|    | 5.1. | Introd  | ucción                                                              | 42 |

|    | 5.2. | Conve   | rtidores reductores con mejora en el factor de potencia             | 43 |

|    |      | 5.2.1.  | Análisis del convertidor reductor en MCD                            | 43 |

|    |      | 5.2.2.  | Análisis del convertidor reductor multifase                         | 4  |

|    |      | 5.2.3.  | Análisis del filtro LC                                              | 5  |

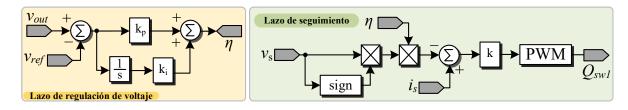

|    |      | 5.2.4.  | Diseño de la estrategia de control                                  | 52 |

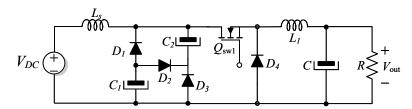

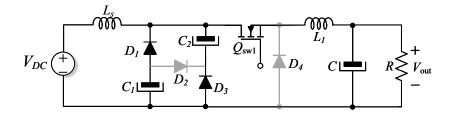

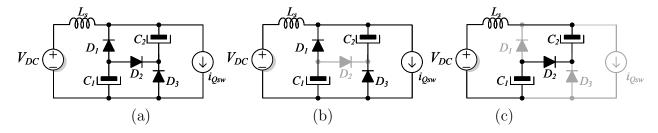

|    | 5.3. | Conve   | rtidor reductor con relación de conversión extendida                | 54 |

|    |      | 5.3.1.  | Análisis del convertidor reductor con relación conversión extendida | 56 |

|    |      | 5.3.2.  | Análisis de la red LCD                                              | 56 |

|    |      | 5.3.3.  | Diseño de la estrategia de control                                  | 58 |

| 6. | Cap  | ítulo V | V: Diseño e implementación del prototipo experimental               | 60 |

|    | 6.1. | Diseño  | o del prototipo experimental del convertidor reductor multifase     | 6. |

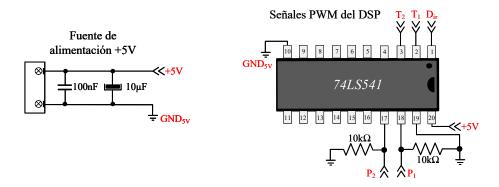

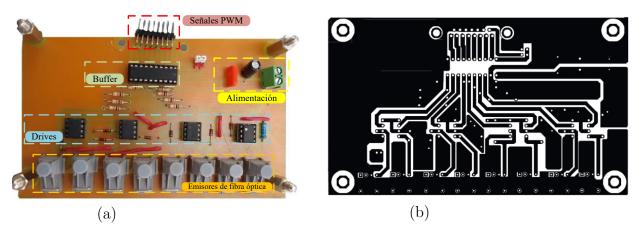

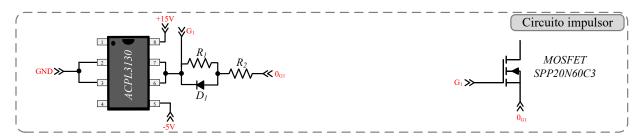

|    |      | 6.1.1.  | Diseño del circuito emisor de fibra óptica                          | 6  |

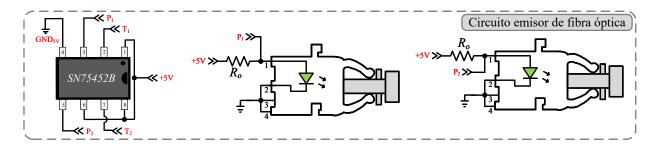

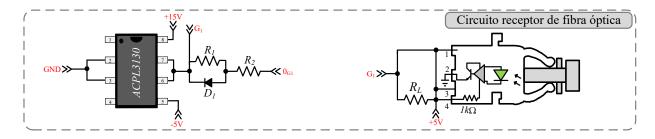

|    |      | 6.1.2.  | Diseño del circuito receptor de fibra óptica                        | 62 |

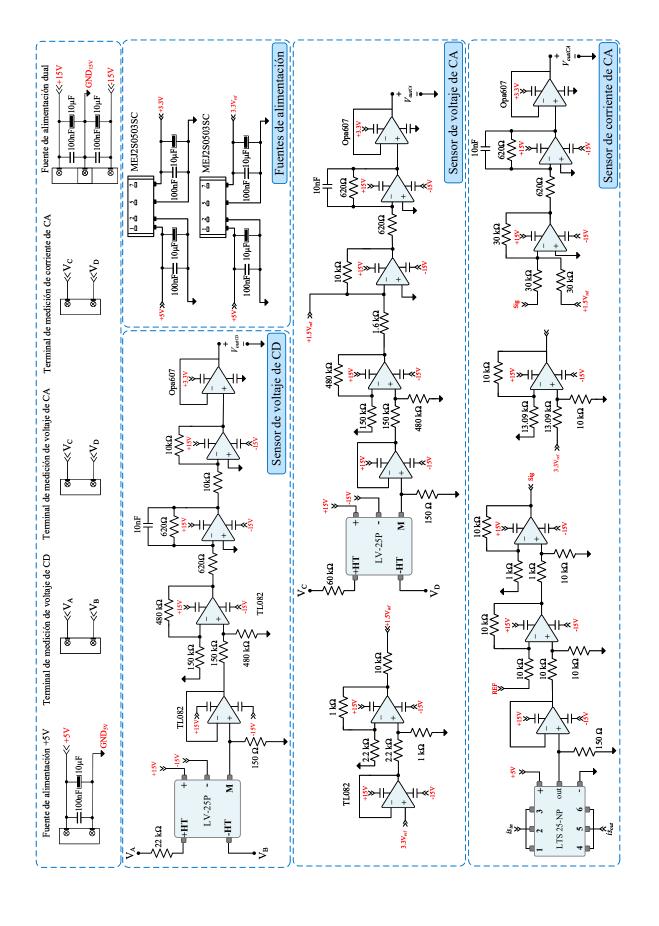

|    |      | 6.1.3.  | Diseño de la tarjeta de sensado de voltaje y corriente              | 65 |

|    |      | 6.1.4.                  | Diseño del convertidor reductor multifase                           | 70   |

|----|------|-------------------------|---------------------------------------------------------------------|------|

|    | 6.2. | Imple                   | mentación de la ley de control                                      | 74   |

| 7. | Cap  | ítulo '                 | VI: Resultados experimentales                                       | 78   |

|    | 7.1. | Result                  | ados de experimentales del convertidor reductor multifase           | . 79 |

|    |      | 7.1.1.                  | Resultados experimentales en lazo abierto                           | 79   |

|    |      | 7.1.2.                  | Resultados experimentales en lazo cerrado                           | 85   |

|    | 7.2. | Result                  | ados experimentales del convertidor reductor con amplia relación de |      |

|    |      | conver                  | rsión                                                               | 91   |

|    |      | 7.2.1.                  | Resultados experimentales en lazo abierto                           | 91   |

|    |      | 7.2.2.                  | Resultados en lazo cerrado                                          | 94   |

| 8. | Con  | clusio                  | nes                                                                 | 99   |

| 9. | Pro  | $\operatorname{ductiv}$ | idad Académica                                                      | 100  |

# Índice de figuras

| 1.  | Clasificación de los métodos para corrección de factor de potencia [3]           | 2  |

|-----|----------------------------------------------------------------------------------|----|

| 2.  | Rectificador de onda completa (a) con filtro L, (b) filtro LCL                   | 22 |

| 3.  | Filtro Valley fill                                                               | 23 |

| 4.  | Clasificación de los convertidores PFC                                           | 24 |

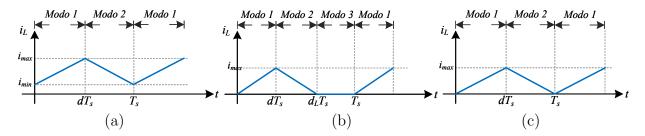

| 5.  | (a) Modo Conducción Continua, (b) Modo Conducción Discontinua y (c)              |    |

|     | Modo Conducción Frontera                                                         | 25 |

| 6.  | Convertidor CA-CD elevador                                                       | 27 |

| 7.  | Convertidor CA-CD elevador de dos fases                                          | 27 |

| 8.  | Convertidor CA-CD reductor-elevador de dos etapas                                | 28 |

| 9.  | Convertidor CA-CD SEPIC                                                          | 29 |

| 10. | Convertidor CA-CD Cuk                                                            | 29 |

| 11. | Convertidor CA-CD Zeta                                                           | 30 |

| 12. | Convertidor CA-CD Reductor                                                       | 30 |

| 13. | Voltaje y corriente de red (a) del convertidor elevador y (b) elevador de dos    |    |

|     | fases                                                                            | 32 |

| 14. | Voltaje y corriente de red (a) del convertidor reductor-elevador y (b) reductor. | 33 |

| 15. | Voltaje y corriente de red (a) del convertidor Cuk y (b) SEPIC                   | 33 |

| 16. | Formas de onda de voltaje y corriente de red (a) con carga puramente             |    |

|     | resistiva, (b) con carga puramente inductiva                                     | 36 |

| 17. | Formas de onda de voltaje y corriente de un rectificador de onda completa.       | 37 |

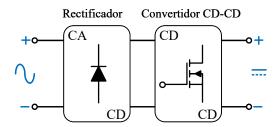

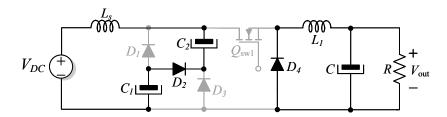

| 18. | Esquema de los convertidores propuesto                                           | 42 |

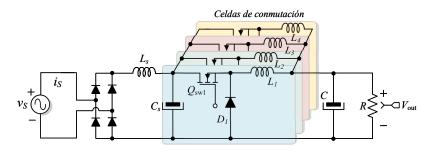

| 19. | Convertidor reductor multifase propuesto                                         | 43 |

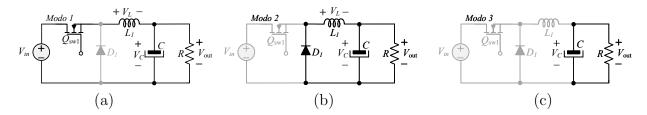

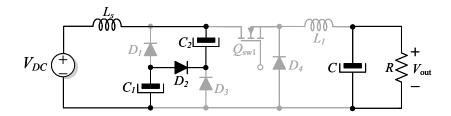

| 20. | Modos de operación del convertidor (a) Modo 1, (b) Modo 2 y (c) Modo 3.          | 44 |

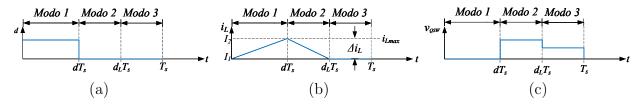

| 21. | Formas de onda del convertidor (a) Ciclo de trabajo, (b) corriente del in-       |    |

|     | ductor $L_1$ y (c) voltaje drenaje-fuente                                        | 4  |

| 22. | Formas de onda del convertidor (a) Voltaje del inductor, (b) corriente del       |    |

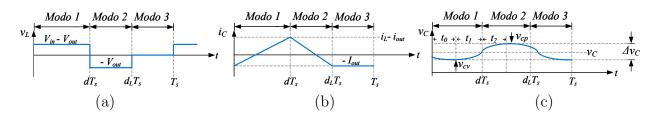

|     | capacitor $i_c$ y (c) voltaje del capacitor                                      | 46 |

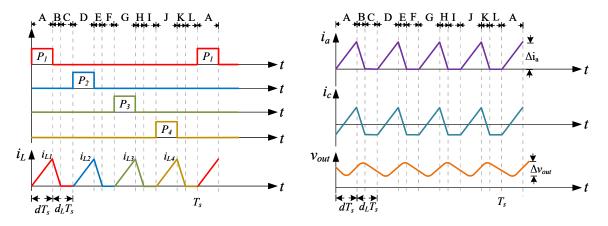

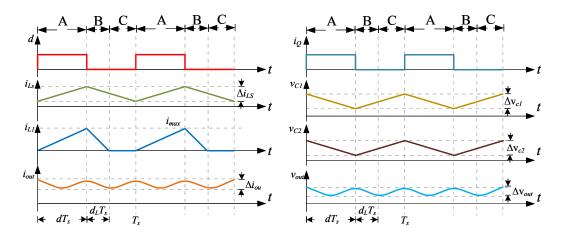

| 23. | Formas de onda del convertidor conmutando un ciclo de trabajo del 25 $\%.$ .     | 48 |

| 24. | Formas de onda del convertidor conmutando un ciclo de trabajo $d=50\%.$          | 50 |

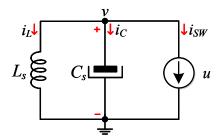

| 25. | Modelado de la red LC con el convertidor                                         | 5. |

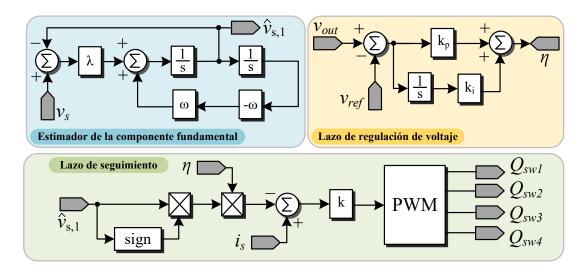

| 26. | Esquema de la ley de control propuesta para el convertidor reductor multifase.   | 54 |

| 27. | Convertidor reductor con relación de conversión extendida                        | 54 |

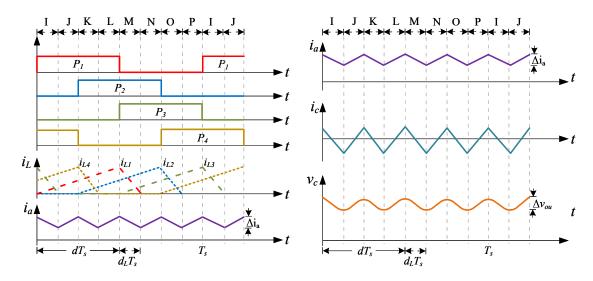

| 28. | Formas de onda del convertidor reductor con relación de conversión extendida.    | 55 |

| 29. | Circuito equivalente del convertidor en el Modo 1                                | 55 |

| 30. | Circuito equivalente del convertidor en el Modo 2                                | 55 |

| 31. | Circuito equivalente del convertidor en el Modo 3                                | 56 |

| 32. | Modelo del filtro LC (a) Modo 1 y (b) Modo 2                                     | 5  |

| 33. | Esquema de la ley de control propuesta para el convertidor reductor de                       |    |

|-----|----------------------------------------------------------------------------------------------|----|

|     | conversión extendida                                                                         | 59 |

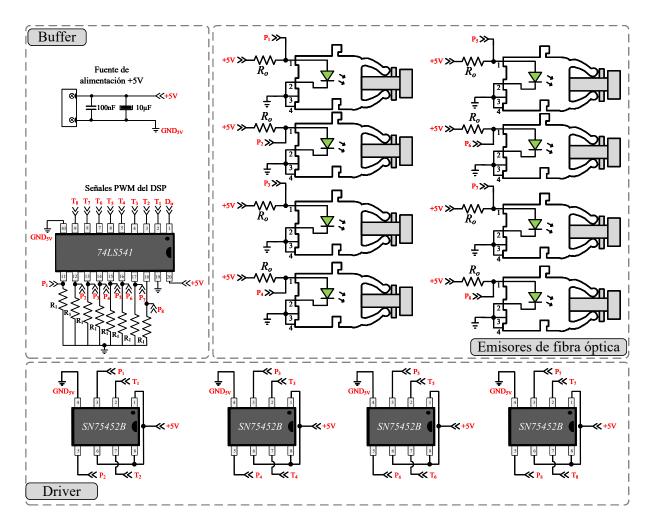

| 34. | Circuito buffer 74LS541                                                                      | 61 |

| 35. | Circuito emisor de fibra óptica.                                                             | 62 |

| 36. | (a) Tarjeta de control implementada. (b) PCB de la tarjeta de control                        | 62 |

| 37. | Circuito simplificado del receptor de fibra óptica.                                          | 63 |

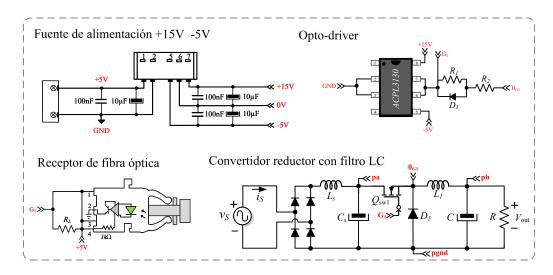

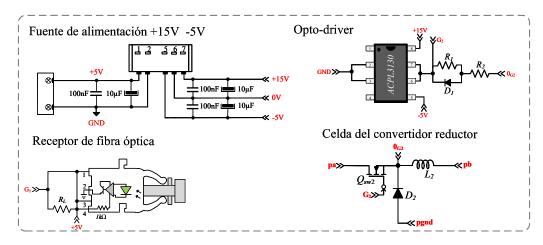

| 38. | Diagrama eléctrico de la tarjeta de control                                                  | 64 |

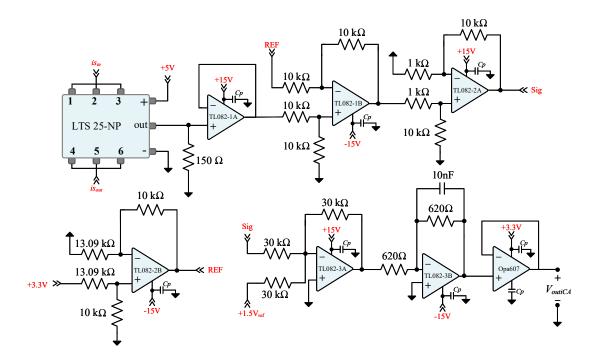

| 39. | Acondicionamiento del sensor de corriente directa                                            | 65 |

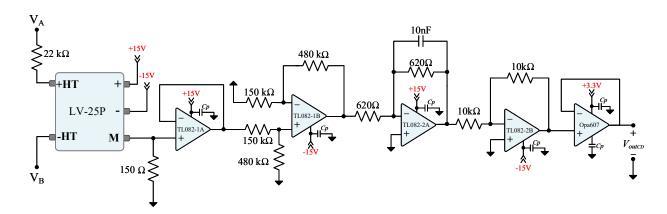

| 40. | Acondicionamiento del sensor de voltaje de CA                                                | 66 |

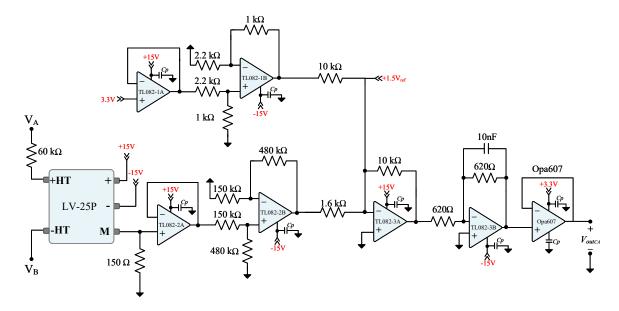

| 41. | Acondicionamiento del sensor de corriente de CA                                              | 67 |

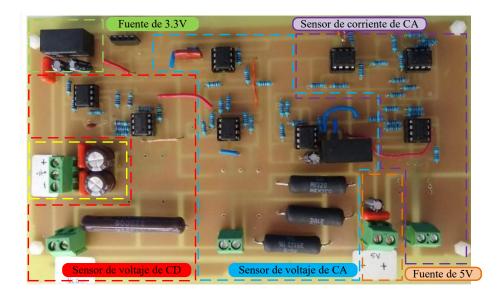

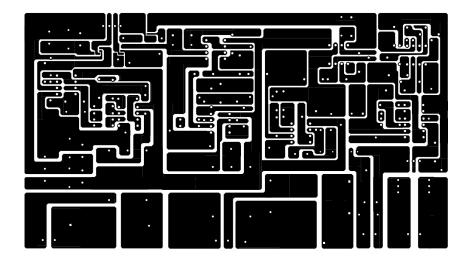

| 42. | Tarjeta de sensado implementada                                                              | 68 |

| 43. | PCB de la tarjeta de sensado implementada                                                    | 68 |

| 44. | Inductor de $500\mu H$ fabricada                                                             | 70 |

| 45. | Circuito eléctrico del circuito impulsor del MOSFET                                          | 71 |

| 46. | Circuito eléctrico del circuito implementado del convertidor reductor con                    |    |

|     | filtro LC                                                                                    | 72 |

| 47. | Circuito eléctrico del circuito implementado de las celdas de conmutación                    |    |

|     | reductoras                                                                                   | 72 |

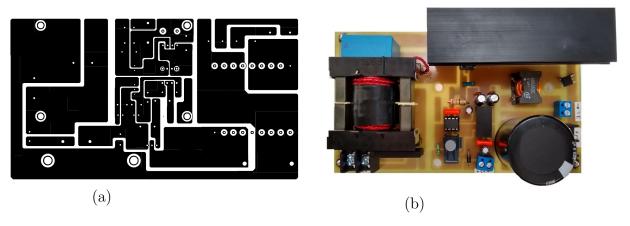

| 48. | (a) PCB del convertidor reductor con filtro LC. (b) Prototipo del convertidor con            |    |

|     | filtro LC                                                                                    | 73 |

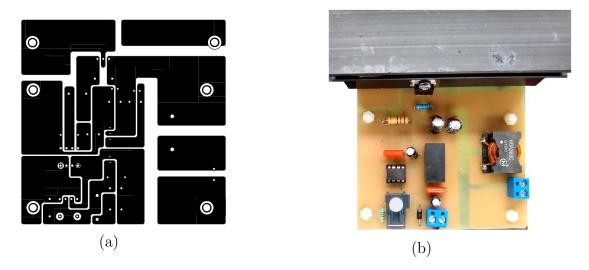

| 49. | (a) PCB del convertidor reductor. (b) Prototipo del convertidor reductor                     | 73 |

| 50. | Modos de conteo                                                                              | 74 |

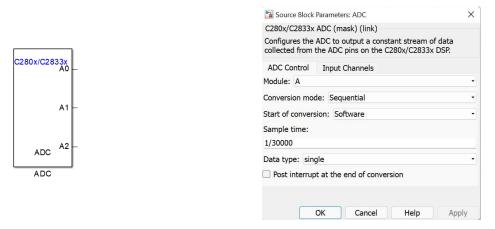

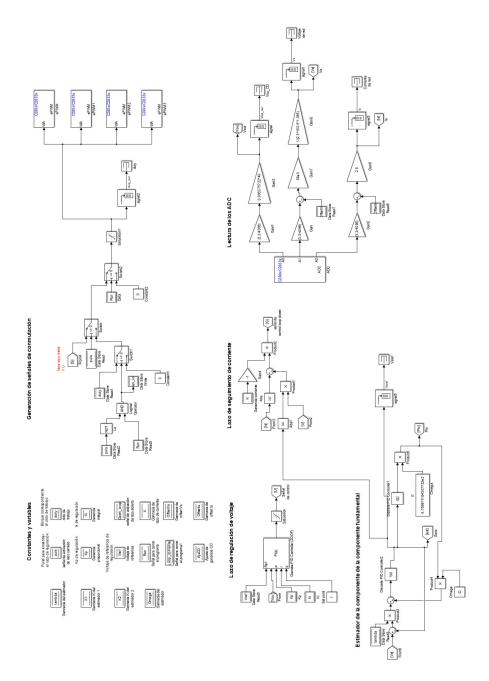

| 51. | Configuración del bloque ADC del DSP TMS320F28335                                            | 75 |

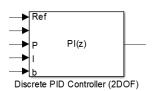

| 52. | Bloque Discrete PID Controller                                                               | 75 |

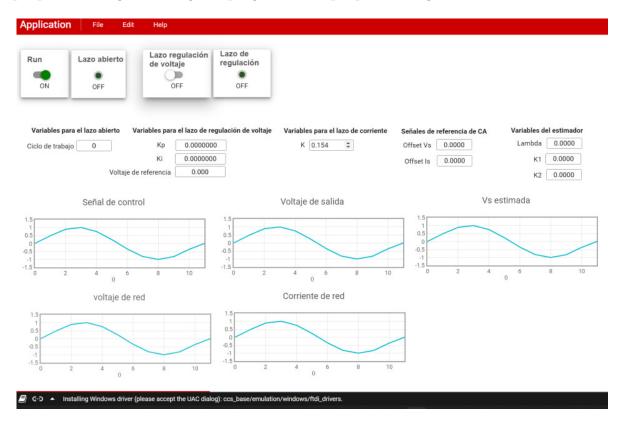

| 53. | Interfaz diseñada                                                                            | 76 |

| 54. | Interfaz diseñada                                                                            | 77 |

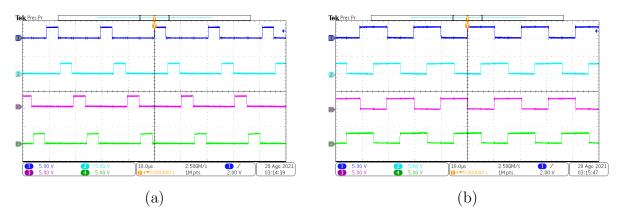

| 55. | Secuencia de pulsos de conmutación con un ciclo de trabajo (a) $20\%$ , (b) $50\%$           | 79 |

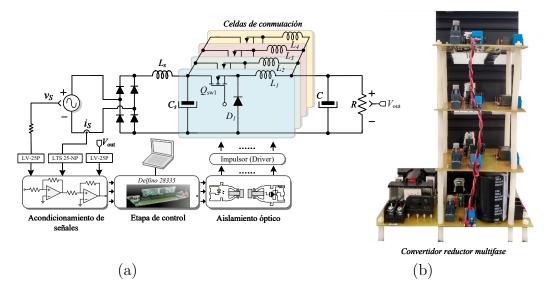

| 56. | Sistema del convertidor reductor multifase                                                   | 80 |

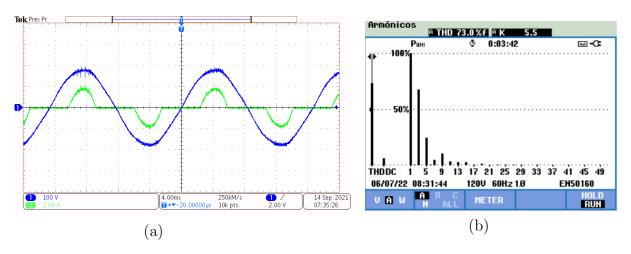

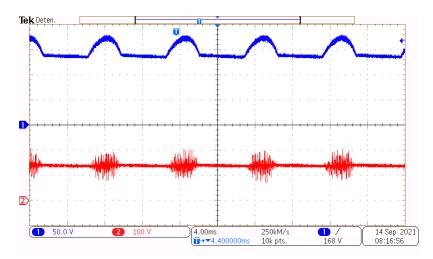

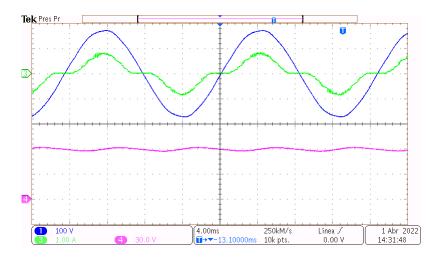

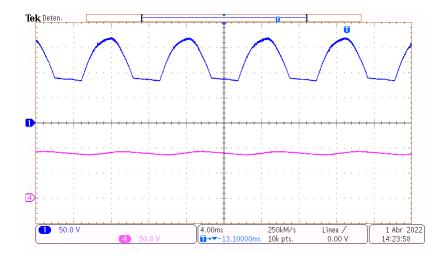

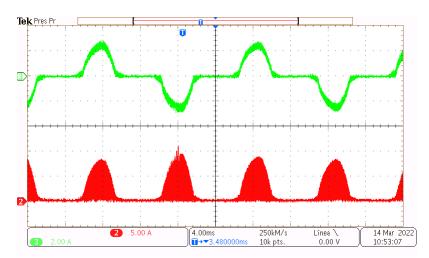

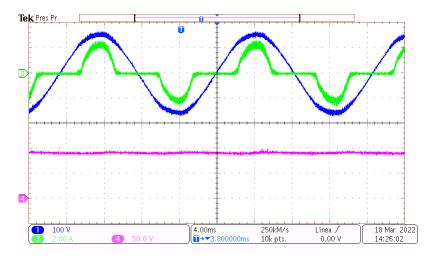

| 57. | (a) Respuesta en estado estacionario de voltaje de la red $v_s$ y corriente de la red        |    |

|     | $i_s$ , (b) espectro en frecuencia de la corriente de la red $i_s$ , con un ciclo de trabajo |    |

|     | ${\rm del}\ 20\%.$                                                                           | 80 |

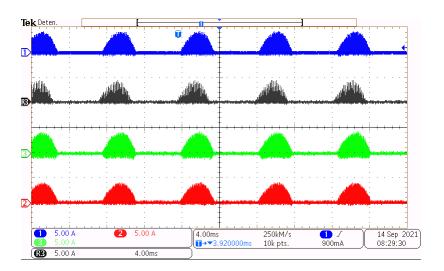

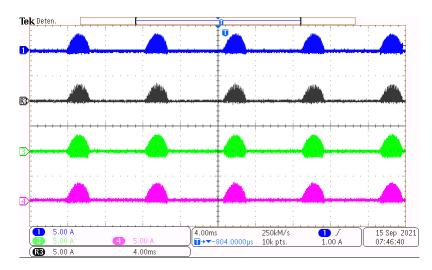

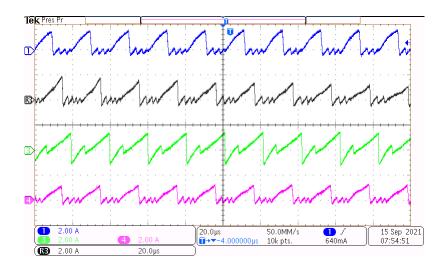

| 58. | Respuesta en estado estacionario de las corrientes a través de los inductores                |    |

|     | $L_1,L_2,L_3$ y $L_4$ , con un ciclo de trabajo del 20 %, a escala de tiempo de $4ms$ .      | 81 |

| 59. | Respuesta en estado estacionario de corrientes a través de los inductores                    |    |

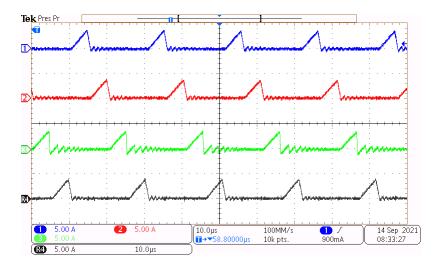

|     | $L_1,L_2,L_3$ y $L_4,$ con un ciclo de trabajo del 20 % a escala de tiempo de $10\mu s.$     | 81 |

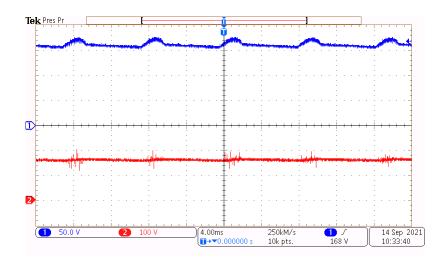

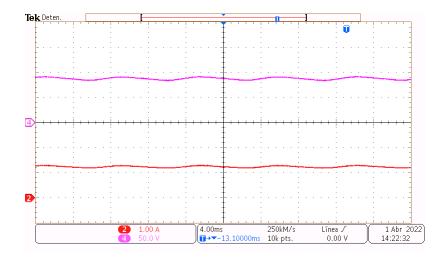

| 60. | Respuesta en estado estacionario de voltaje capacitor $C_s$ y voltaje de salida              |    |

|     | $v_{out}$ , con un ciclo de trabajo del 20 %                                                 | 82 |

| 61. | Respuesta en estado estacionario de voltaje $v_{out}$ y corriente $i_{out}$ de salida,       |    |

|     | con un ciclo de trabajo del $20\%$                                                           | 82 |

| 62. | (a) Respuesta en estado estacionario de voltaje de red $v_s$ y corriente de red $i_s$ .   |    |

|-----|-------------------------------------------------------------------------------------------|----|

|     | (b) Espectro en frecuencia de la corriente de red $i_s$ , con un ciclo de trabajo del     |    |

|     | 50%                                                                                       | 83 |

| 63. | Respuesta en estado estacionario de corrientes a través de los inductores                 |    |

|     | $L_1,L_2,L_3$ y $L_4,$ con un ciclo de trabajo del 50 % a escala de tiempo de $4ms.$      | 83 |

| 64. | Respuesta en estado estacionario de corrientes a través de los inductores                 |    |

|     | $L_1,L_2,L_3$ y $L_4,$ con un ciclo de trabajo del 50 %, a escala de tiempo de $10\mu s.$ | 84 |

| 65. | Respuesta en estado estacionario de voltaje del capacitor $C_s$ y voltaje de              |    |

|     | salida $v_{out}$ del convertidor reductor multifase, con un ciclo de trabajo del          |    |

|     | 50%                                                                                       | 84 |

| 66. | Respuesta en estado estacionario de voltaje $v_{out}$ y $i_{out}$ corriente de salida     |    |

|     | del convertidor reductor multifase, con un ciclo de trabajo del 50 %                      | 85 |

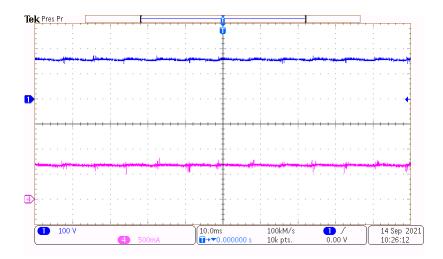

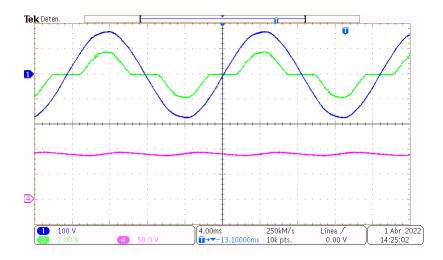

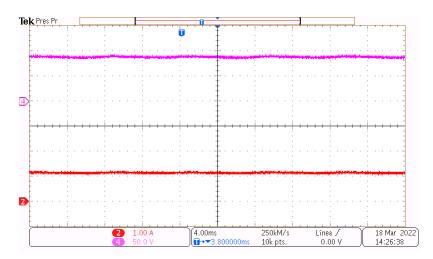

| 67. | Respuesta en estado estacionario de voltaje de red $v_s$ , corriente de red $i_s$ y       |    |

|     | voltaje de salida $v_{out}$                                                               | 85 |

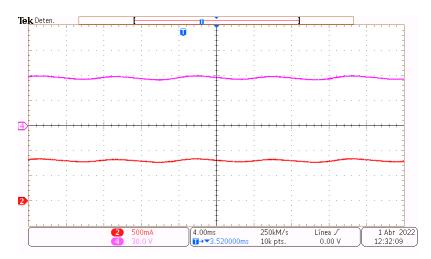

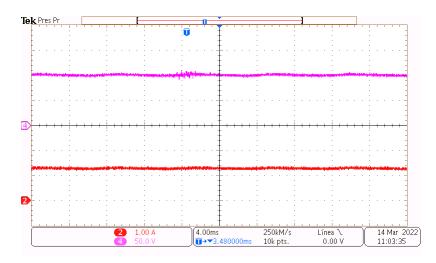

| 68. | Respuesta en estado estacionario de voltaje de los capacitores $C_s$ y $C$ , con          |    |

|     | un voltaje de referencia de 60V                                                           | 86 |

| 69. | Respuesta en estado estacionario del voltaje y corriente de salida, con un                |    |

|     | voltaje de referencia de 60V                                                              | 86 |

| 70. | Respuesta en estado estacionario de voltaje de red $v_s$ , corriente de red $i_s$ y       |    |

|     | voltaje de salida $v_{out}$                                                               | 87 |

| 71. | Respuesta en estado estacionario de voltaje de los capacitores $C_s$ y $C$ , con          |    |

|     | un voltaje de referencia de 90V                                                           | 88 |

| 72. | Respuesta en estado estacionario de voltaje $v_{out}$ y corriente de salida $i_{out}$ ,   |    |

|     | con un voltaje de referencia de 90V                                                       | 88 |

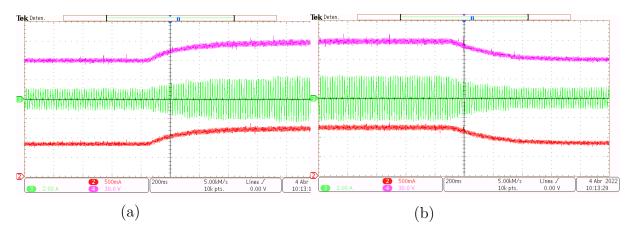

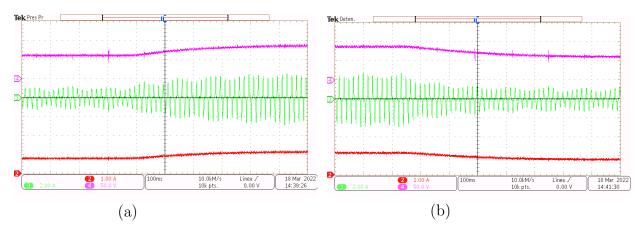

| 73. | Respuesta dinámica del convertidor reductor multifase en lazo cerrado, ante               |    |

|     | un cambio de voltaje de referencia (a) de 60V a 90V, (b) de 90V a 60V                     | 89 |

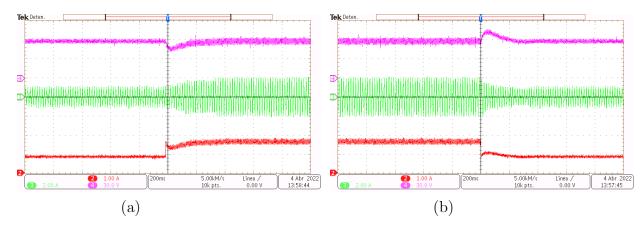

| 74. | Respuesta dinámica del convertidor reductor multifase ante un cambio de                   |    |

|     | carga (a) de 73 $\Omega$ a 37 $\Omega$ , (b) de 37 $\Omega$ a 73 $\Omega$                 | 90 |

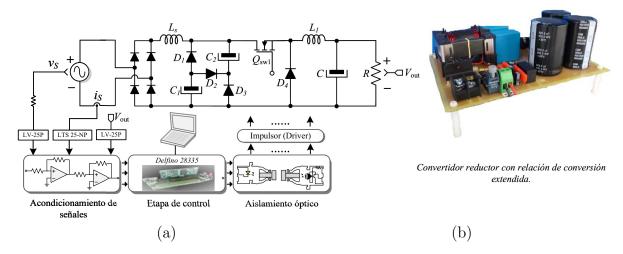

| 75. | Sistema del convertidor reductor con relación de conversión extendida                     | 91 |

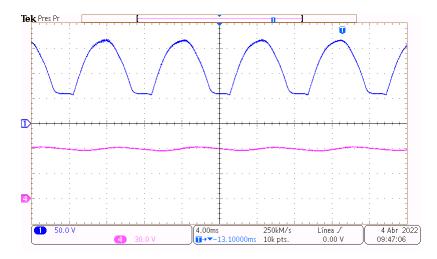

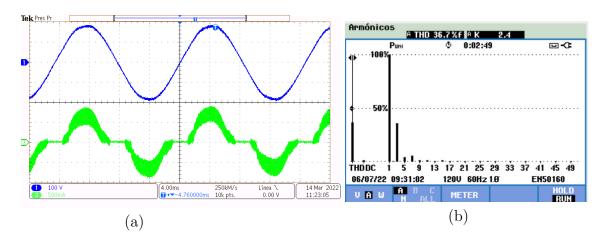

| 76. | (a) Respuesta en estado estacionario del convertidor reductor con relación                |    |

|     | de conversión extendida voltaje y corriente de red, (b) espectro en frecuencia            |    |

|     | de la corriente de red                                                                    | 92 |

| 77. | Respuesta en estado estacionario de voltaje $v_{out}$ y corriente $i_{out}$ de salida     |    |

|     | del convertidor reductor con relación de conversión extendida con un ciclo                |    |

|     | de trabajo del $30\%$                                                                     | 92 |

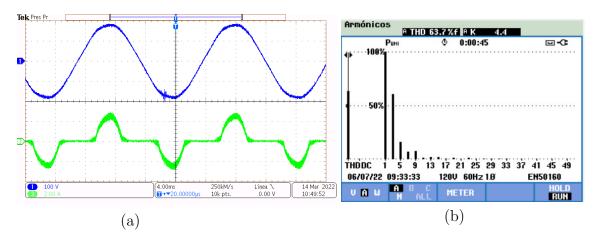

| 78. | Respuesta en estado estacionario del convertidor reductor con relación de                 |    |

|     | conversión extendida (a) voltaje $v_s$ y corriente $i_s$ de red, con un ciclo de          |    |

|     | trabajo del $60\%$ , (b) espectro en frecuencia de la corriente de red                    | 93 |

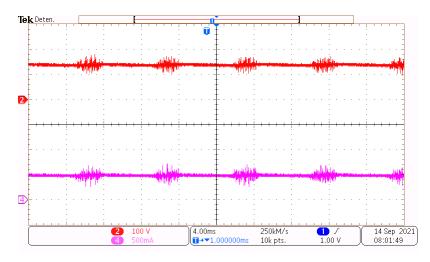

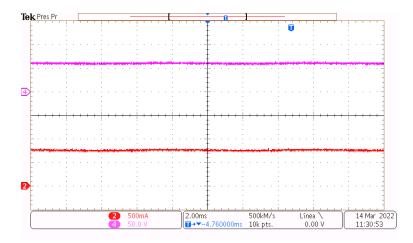

| 79. | Respuesta en estado estacionario del convertidor reductor con relación de                 |    |

|-----|-------------------------------------------------------------------------------------------|----|

|     | conversión extendida corriente de red $i_s$ y del inductor $L_1$ , con un ciclo de        |    |

|     | trabajo del 60 %                                                                          | 93 |

| 80. | Respuesta en estado estacionario de voltaje $v_{out}$ y corriente de salida $i_{out}$     |    |

|     | del convertidor reductor con relación de conversión extendida, con un ciclo               |    |

|     | de trabajo del 60 %                                                                       | 94 |

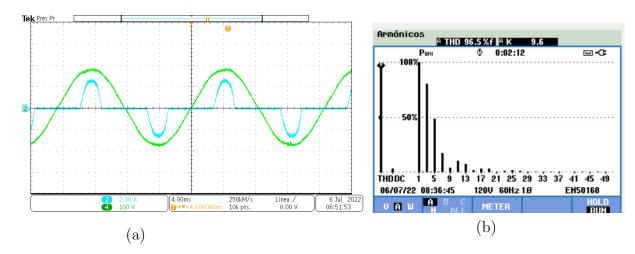

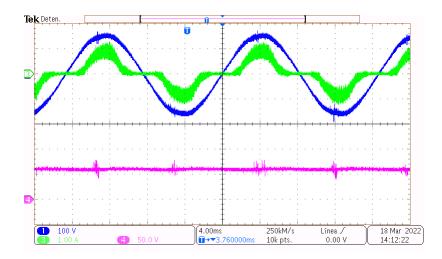

| 81. | Respuesta en estado estacionario de voltaje $v_s$ y corriente de red $i_s$ , y voltaje    |    |

|     | de salida $v_{out}$ del convertidor reductor con relación de conversión extendida,        |    |

|     | con un voltaje de referencia de 60V                                                       | 95 |

| 82. | Respuesta en estado estacionario de voltaje $v_{out}$ y corriente de salida $i_{out}$ del |    |

|     | convertidor reductor con relación de conversión extendida, con un voltaje                 |    |

|     | de referencia de 60V                                                                      | 95 |

| 83. | Respuesta en estado estacionario de voltaje $v_s$ y corriente de red $i_s$ y voltaje      |    |

|     | de salida $v_{out}$ del convertidor reductor con relación de conversión extendida,        |    |

|     | con un voltaje de referencia de 90V                                                       | 96 |

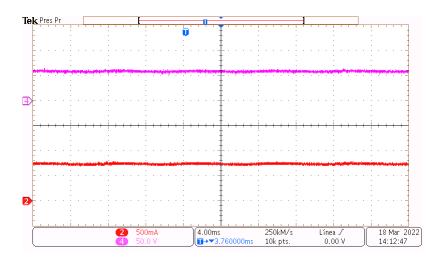

| 84. | Respuesta en estado estacionario de voltaje $v_{out}$ y corriente de salida $i_{out}$     |    |

|     | del convertidor reductor con un voltaje de referencia de 90V                              | 96 |

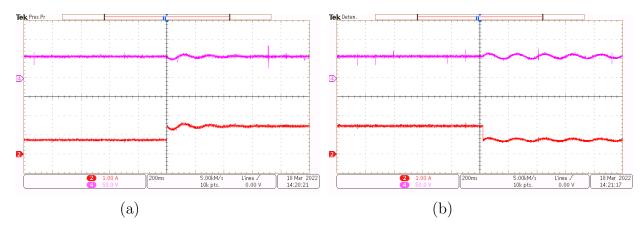

| 85. | Respuesta dinámica del convertidor reductor con relación de conversión                    |    |

|     | extendida, ante un cambio de voltaje (a) de 60V a 90V, (b) de 90V a 60V.                  | 97 |

| 86. | Respuesta dinámica del convertidor reductor con relación de conversión                    |    |

|     | extendida ante un cambio de voltaje (a) de 60V a 90V. (b) de 90V a 60V.                   | 97 |

1. Introducción

El suministro eléctrico a cargas de DC desde una red eléctrica de corriente alterna, AC, se realiza generalmente en dos etapas. Primeramente el voltaje de AC de la red se convierte en un voltaje de corriente directa, DC, (proceso de rectificación) y después se adapta al voltaje de la carga con un convertidor DC-DC con o sin aislamiento galvánico.

En el caso más sencillo, la rectificación puede realizarse usando solamente rectificadores de diodos con capacitor de alisamiento de salida e inductores en el lado de AC o de DC. Estos sistemas tienen efectos adversos sobre la red eléctrica y un voltaje de DC de salida no regulado. Los efectos sobre la red eléctrica son un bajo factor de potencia FP, es decir, ocasionan distorsión armónica y desplazamiento de la forma de onda de la corriente fundamental de la red con respecto del voltaje de red.

Actualmente existen normas que imponen limites al contenido armónico que una carga puede inyectar hacia la red eléctrica, entre las cuales se encuentran la IEC 61000-3-2 e IEEE519-201. El contenido armónico inyectado a la red debe ser regulado, debido a que puede provocar una reducción en el factor de potencia del sistema, calentamiento en los dispositivos e interferencia electromagnética.

Una vertiente de las investigaciones publicadas en la literatura especializada se ha enfocado en corregir el FP. Estas investigaciones consisten en la propuesta de diferentes convertidores, modificaciones a los existentes, y controladores para asegurar que la corriente que demanda una carga contenga solamente componente a la frecuencia fundamental de la red, y esté en fase con el voltaje.

En este trabajo de tesis se presenta el análisis, diseño e implementación de dos topologías de convertidores CA-CD empleadas en aplicaciones de corrección del factor de potencia. Las topologías propuestas están conformadas por una etapa de CA-CD seguida de una etapa de CD-CD. Las topologías propuestas se basan en el principio de operación de un convertidor reductor convencional. Sin embargo, se incorporan algunas modificaciones en su estructura para ser empleadas en aplicaciones de corrección de factor de potencia.

La estructura de este documento se divide en seis capítulos, en donde primeramente se explican las generalidades de este proyecto. En el segundo capitulo se presenta una revisión del estado del arte enfocado en convertidores CA-CA utilizados en aplicaciones de corrección de factor de potencia. El tercer capitulo se presenta el marco teórico del trabajo de tesis. En los capítulos cuatro y cinco se describen y analizan las dos topologías propuestas. Finalmente, en el capitulo seis se presentan los resultados experimentales en lazo abierto y lazo cerrado.

2. Capítulo I: Generalidades del proyecto

# 2.1. Planteamiento del problema

El suministro de energía a cargas de corriente directa CD desde la red eléctrica de CA es una práctica común en la actualidad, debido a la gran cantidad de dispositivos electrónicos que se usan día a día.

Para llevar a cabo el proceso de conversión de energía de CA a CD es común utilizar un puente rectificador no controlado seguido de un capacitor de alisamiento. Sin embargo, aunque la construcción de este tipo de topología es simple, tiene ciertas desventajas en términos de la calidad de la energía, ya que la corriente de la red tiene un alto contenido armónico y, en consecuencia un bajo factor de potencia.

En la literatura especial izadas se han reportado distintas topologías de convertidores CA-CD que presentan ventajas en términos de regulación de voltaje y calidad de la energía. En este trabajo de tesis se estudian convertidores de electrónica de potencia CA-CD. Así, se proponen, diseñan, analizan y comprueban soluciones de convertidores CA-CD en lazo abierto y lazo cerrado para la mejora del factor de potencia. Las soluciones propuestas tienen como objetivo de proveer a la carga una potencia nominal de CD y realizar la corrección del factor de potencia. Se valida de forma experimental tanto en lazo abierto como en lazo cerrado el funcionamiento de los convertidores propuestos.

### 2.2. Justificación

El desarrollo de este trabajo de tesis, contribuye al área de electrónica de potencia; especialmente con desarrollos tecnológicos aplicados en el aprovechamiento eficiente de la energía en sistemas de conversión CA-CD.

Este trabajo de tesis tiene relevancia en eficiencia energética debido a que una de sus aplicaciones es el suministro de energía a cargas de corriente directa, con mayor aprovechamiento de energía.

La aportación del presente trabajo de tesis al desarrollo tecnológico es en el estudio, desarrollo y validación de sistemas conversión de energía de CA-CD que emplean una etapa de CD-CD. Dichos sistemas tienen aplicaciones para la mejora del factor de potencia y la disminución de la distorsión armónica total.

# 2.3. Objetivo general y objetivos específicos

### Objetivo General

Estudiar configuraciones y controladores para la mejora del factor de potencia para convertidores CA-CD formados por rectificadores no controlados sin capacitor y convertidor CD-CD.

### Objetivos específicos

- Revisar el estado del arte de convertidores CA-CD y controladores para la mejora de factor de potencia.

- Analizar y diseñar soluciones de convertidores CD-CD en lazo abierto y lazo cerrado para la mejora del factor de potencia.

- Estudiar y proponer controladores para la mejora del factor de potencia en convertidores CA-CD.

- Validar por medio de simulación numérica y experimentalmente las soluciones propuestas de convertidores CD-CD en lazo abierto y lazo cerrado.

3. Capítulo II: Estado del arte

# 3.1. Métodos para la corrección del factor de potencia

Hoy en día los convertidores de electrónica de potencia de corriente alterna a corriente directa (CA-CD), también llamados rectificadores, son muy utilizados en especial por el gran número de aplicaciones que los utilizan tanto industriales como residenciales [1], [2]. Sin embargo, el uso de estos sistemas puede tener efectos adversos sobre la red eléctrica y un voltaje de CD de salida no regulado. Los efectos sobre la red eléctrica son un bajo factor de potencia (FP), alta distorsión armónica y desplazamiento de la forma de onda de la corriente fundamental de la red con respecto del voltaje de red.

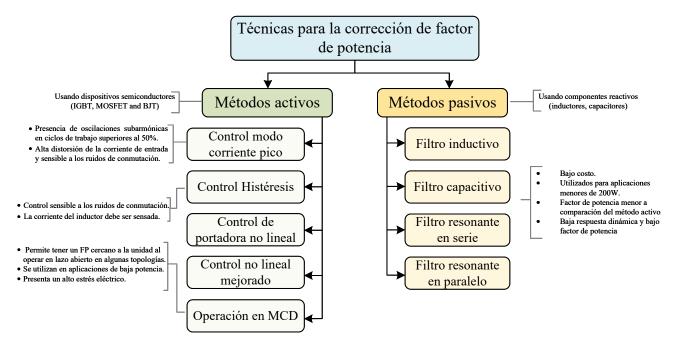

En la literatura se han reportado diferentes técnicas para realizar la corrección del FP en convertidores CA-CD. En la Figura 1, se muestra un diagrama de una clasificación de las diferentes técnicas que se han usado para la corrección del FP. Éstas se pueden dividir en dos grupos; métodos pasivos y activos [3].

Figura 1: Clasificación de los métodos para corrección de factor de potencia [3].

# 3.2. Métodos pasivos para la corrección del factor de potencia

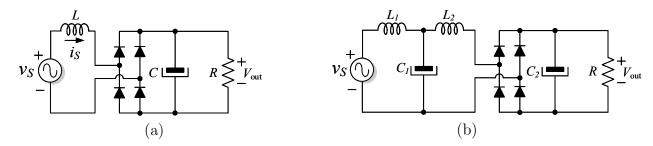

Los métodos pasivos consisten en utilizar elementos como inductores y capacitores con el fin de actuar como filtros pasa bajas. En Figura 2 (a), se muestra uno de los filtros más utilizados. Este filtro está conformado por un inductor, el cual se coloca de lado de la red eléctrica de CA con el propósito de mitigar las componentes armónicas inyectadas hacia la red.

Aunque esta estructura permite tener un FP alrededor del 0.7, presenta ciertas desventajas al emplearse en aplicaciones de alta potencia. Esto se debe, a que se requiere un valor de inductor grande, lo que introduce pérdidas de potencia y por consecuencia una disminución en el rendimiento dinámico del convertidor [4]-[6].

Figura 2: Rectificador de onda completa (a) con filtro L, (b) filtro LCL.

Una solución atractiva para resolver estos problemas es utilizar un filtro LCL, como el que se muestra en la Figura 2 (b). Este filtro tiene el mismo propósito de reducir la distorsión armónica inyectada a la red. En este caso se tiene la ventaja de requerir valores de inductancias más pequeñas, lo que resulta en una disminución en el costo y tamaño del sistema en aplicaciones de alta potencia [7].

En [9]-[11] se han estudiado filtros LCL para ser utilizados en aplicaciones de PFC (siglas en inglés de Power Factor Corretion). Algunos de los principales inconvenientes que tienen estos tipos de configuraciones, están relacionados con los efectos de resonancia [6]. Uno de los métodos reportados en la literatura para resolver los problemas relacionados con la resonancia, es mediante amortiguación pasiva debido a su simplicidad y bajo costo [8], [12], [13], [14]. Sin embargo, el uso de este método de amortiguación puede causar varios inconvenientes que están relacionados con el rendimiento y eficiencia del sistema [7], dado que introducen disipación de energía.

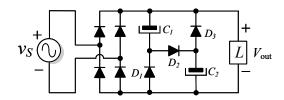

Otros de los filtros pasivos reportados en la literatura que se han utilizado en aplicaciones de PFC, se muestra en la Figura 3, [15], [16], [18]. Este filtro tiene la ventaja sobre los dos filtros anteriormente mencionados, de no requerir inductores voluminosos, por lo que su tamaño puede ser menor. El filtro Valley Fill se conforma por un arreglo de diodos y capacitores como se observa en la Figura 3.

Figura 3: Filtro Valley fill.

El propósito de agregar este filtro es incrementar el periodo de tiempo, donde el convertidor consume corriente de la red eléctrica [17]. El resultado es una reducción del ángulo de no conducción que ocurre en la forma de onda de corriente de red durante el cruce por cero. Esto trae consigo una reducción en la distorsión armónica total y por consecuencia un incremento en el valor de FP, debido a la relación que existe entre el THD (siglas en inglés de Total Harmonic Distortion) y FP como se muestra en (1) [87].

$$FP = \frac{\cos(\theta)}{\sqrt{1 + (THD)^2}}\tag{1}$$

donde  $\theta$  es el ángulo de desfase entre el voltaje y la corriente de red.

## 3.3. Métodos activos para la corrección del factor de potencia

Aún cuando los métodos pasivos son ampliamente utilizados para realizar la corrección del FP en convertidores CA-CD. Varios autores optan por utilizar el método activo en aplicaciones de alta potencia. Esto se debe, a que los métodos activos pueden presentar una mejor eficiencia y un factor de potencia unitario. Los métodos activos consisten en utilizar convertidores CD-CD, con el propósito de hacer que el sistema emule el comportamiento de una resistencia [19], [20]. Esto trae como consecuencia que el factor de potencia del convertidor sea cercano a la unidad.

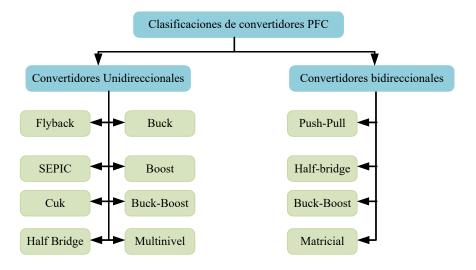

Los métodos activos se pueden clasificar según el flujo de potencia, que puede ser unidireccional o bidireccional, el número de etapas o el tipo de aislamiento [21]. En la Figura 4, se muestra la clasificación de los métodos activos de acuerdo al flujo de potencia. Los convertidores unidireccionales están conformados por una etapa rectificadora en serie con una etapa de conversión de energía CD-CD, y su principal característica es que solo permiten el flujo de energía en un sólo sentido [22].

Algunas de las topologías de convertidores CD-CD que se han utilizado en convertidores unidireccionales, son el convertidor boost, buck, buck-boost, SEPIC, Cuk y multinivel, como se puede observar en la Figura 4. El convertidor multinivel es el que mayores ventajas presenta, ya que tiene un bajo estrés eléctrico en los dispositivos semiconductores, una alta eficiencia y además puede ser usado en aplicaciones de alta potencia [22].

Figura 4: Clasificación de los convertidores PFC.

Las aplicaciones de estos tipos de convertidores, son en sistemas de alimentación, variadores de velocidad para ventiladores, compresores, y sistemas de aire acondicionado. Además, cada vez más están tomando importancia en sistemas de generación de energía alternativa como en sistemas fotovoltaicos y sistemas de carga para vehículos eléctricos [22], [49], [24], [25].

Por otro lado, los convertidores bidireccionales, a diferencia de los convertidores unidireccionales no emplean el uso de un puente de diodos, ya que los sustituyen por MOSFET (siglas en inglés de Metal-Oxide-Semiconductor Field-Effect-Transistor) o IGBTs (siglas en inglés de Insulated Gate Bipolar Transistor), para realizar la conversión de energía de CA-CD. Debido a esta característica estos convertidores permiten el flujo de energía en los dos sentidos [22]. Algunas de las aplicaciones en las que se han usado este tipo de convertidores son en sistemas de carga de baterías, sistemas de energía ininterrumpida (UPS), grúas, entre otros [22], [25].

### 3.3.1. Convertidores operados en Modo de Conducción Continua

Otra de las maneras en que se pueden clasificar los métodos activos es dependiendo el modo de operación del convertidor. Existen tres tipos de operación; Modo de Conducción Continua (MCC), Modo de Conducción Discontinua (MCD) y Modo de Conducción Frontera (MCF). Estos métodos conciernen a la forma de onda de la corriente del inductor. Al operar en MCC la corriente del inductor es continua en estado estacionario. Mientras en MCD la corriente del inductor es cero durante una fracción de periodo de conmutación, como se observa en la Figura 5 (b). Los convertidores operados en modo de conducción frontera la forma de onda de corriente de toma el valor de cero en un pequeño instante de

tiempo como se muestra en la Figura 5 (c).

Figura 5: (a) Modo Conducción Continua, (b) Modo Conducción Discontinua y (c) Modo Conducción Frontera.

Los convertidores PFC operados en MCC tienen la ventaja de tener un FP unitario y menor índice de THD en comparación a los convertidores PFC operados en MCD. Sin embargo, al operar los convertidores PFC en MCC se tiene la desventaja de requerir estrategias de control para asegurar el FP cercano a la unidad.

En la literatura se han reportado diferentes estrategias de control para realizar la corrección del FP [26] - [32]. En [26] se estudia un controlador basado en una modulación de histéresis. En este controlador los autores proponen determinar el intervalo de tiempo ideal entre el encendido del interruptor y el momento en que la corriente de entrada excede la corriente de referencia. Esto permite que la corriente de entrada oscile alrededor de una corriente de referencia con una frecuencia fija. Por esta característica es que el controlador propuesto puede evitar los problemas relacionados con la frecuencia de conmutación variable que están relacionados con el control de histéresis convencional [26]. El controlador se implementó en un convertidor de tipo elevador operado en MCC. Se reporta que el nivel de THD de corriente fue 1.8 % y el FP es cercano a la unidad.

Otro de los controladores utilizados en convertidores PFC, es el control de corriente máxima [27], [28], [29]. Este controlador tiene el propósito de hacer que la corriente que fluye a través del inductor siga una señal de referencia. En este caso, la señal de referencia se genera a partir de multiplicar una señal a escala del voltaje rectificado, con una señal de error que se obtiene al sensar el voltaje salida del convertidor [30]. Sin embargo, este controlador tiene un inconveniente que está relacionado con el nivel de THD de corriente de red, debido a que la corriente de entrada presenta un ángulo de no conducción durante el cruce por cero [27].

En [31], se propone un control repetitivo para un precompensador de factor de potencia, implementado en un convertidor elevador. El objetivo es garantizar que el factor de potencia sea cercano a la unidad, a pesar de la distorsión armónica en el voltaje de la red. El controlador consta de la interconexión en cascada de lazos de control interno y

externo. El lazo de control interno tiene como principal función de asegurar que el factor de potencia sea cercano a la unidad, y está conformado por un esquema repetitivo más un término proporcional. El objetivo del control repetitivo es compensar las componentes armónicos impares de la distorsión periódica del voltaje de red. El lazo de control externo está formado por un término proporcional de ancho de banda limitado más un término integral. El principal objetivo de este lazo de control es garantizar la regulación de voltaje de salida del convertidor. Los resultados experimentales del controlador demuestran que el convertidor presenta un FP cercano a la unidad, además de compensar los armónicos 3°, 5° y 7°.

En [32] se estudian tres controladores basados en el concepto de control de carga, empleados en aplicaciones de corrección del factor de potencia. Los controladores se emplean en un convertidor elevador de dos fases. El propósito de los controladores es asegurar que la corriente a través de cada celda de conmutación se distribuya uniformemente. Los controladores representan una solución atractiva porque evitan el uso de sensores de corriente convencionales que son remplazados por transformadores de corriente, que resultan ser más económicos. Los resultados experimentales demuestran que al emplear estos controladores se puede tener factores de potencia cercanos a la unidad, además de equilibrar la corriente a través de los inductores cuando se usan en un convertidor con n celdas de conmutación.

### 3.3.2. Convertidores operados en Modo de Conducción Discontinua

A diferencia de los convertidores PFC operados en MCC, los convertidores operados en MCD no requieren estrategias de control para realizar la corrección del factor de potencia. Esto se debe a que en este modo de operación algunas topologías pueden realizar la corrección del factor de potencia al operar en lazo abierto.

#### Convertidor elevador

Uno de los convertidores más empleados en aplicaciones de PFC, es el convertidor elevador [33], [34], [35], [36]. Este convertidor se conforma por un rectificador de onda completa, seguido de un convertidor CD-CD de tipo elevador, como se observa en la Figura 6. Esta topología se ha reportado que se ha empleado en aplicaciones de PFC, cuando opera tanto en MCC o MCD [37], [38], [39], [40]. Sin embargo, el convertidor al operar en MCC requiere leyes de control para tener un FP cercano a la unidad, por lo que se incrementa la complejidad de su implementación [41].

El convertidor elevador en MCD, tiene la característica de realizar la corrección de factor de potencia de forma inherente [42], [41]. Esto se debe a que la topología crea una envolvente en la corriente de la red, la cual se encuentra en fase con el voltaje [42]. Al operar en MCD no se presenta el problema de conmutación dura en el interruptor, además

Figura 6: Convertidor CA-CD elevador.

de que no tiene pérdidas de potencia asociadas a la recuperación inversa del diodo [43], [44].

Dos de los inconvenientes que tiene el convertidor elevador, están relacionados con la corriente de la red. Lo cual, se debe a que la topología tiene un alto THD y rizado en la corriente de entrada [43]. Además, los dispositivos semiconductores se encuentran sometidos a un alto estrés eléctrico, por lo que sólo se utiliza en aplicaciones de baja potencia [45], [42], [70].

#### Convertidor elevador de dos fases

El convertidor elevador de dos fases propone incorporar una celda de conmutación adicional, como se observa en la Figura 7. El funcionamiento del convertidor es similar al convertidor elevador convencional, pero en este caso cada celda se encuentra conmutando con un desplazamiento de 180 grados cada una respecto de la otra [48], [47].

Figura 7: Convertidor CA-CD elevador de dos fases.

En esta topología se presenta una reducción en el rizo de corriente de entrada ya que, al emplear celdas de conmutación desfasadas entre sí, el rizo de corriente se tiende a cancelar [49]. Por esta característica se puede reducir el tamaño el tamaño de filtro EMI (de las siglas en inglés Electro Magnetic Interference) de entrada [47]. Además, el rizo de corriente de salida se puede reducir significativamente, lo que implica una reducción en el volumen de capacitor de salida [50]. Al emplear celdas de conmutación en paralelo, se tiene una

reducción en estrés eléctrico en los dispositivos semiconductores, por lo que el convertidor se puede ser utilizado en aplicaciones de alta potencia [51], [52].

#### Convertidor reductor-elevador

El convertidor reductor-elevador mostrado en la Figura 8, es otra de las topologías que se han utilizado para aplicaciones de PFC [53],[54], [55], [56]. El convertidor reductor-elevador convencional tiene la desventaja de tener un voltaje de salida invertido, lo que lo hace inadecuado en aplicaciones de alta potencia [57]. Se han reportado diferentes trabajos, los cuales abordan este problema. En [58] se presenta un convertidor reductor elevador en cascada, el cual tiene un voltaje de salida no invertido, debido a la relación de ganancia que tiene.

Sin embargo, uno de los principales inconvenientes que tiene es el alto estrés eléctrico e incluso mayor al que puede presentar el convertidor elevador [59]. Además, el convertidor reductor-elevador al operar en altas frecuencias de conmutación presenta una reducción en el tiempo de encendido de los interruptores. Lo que resulta un aumento en las pérdidas de potencia originadas por el proceso de conmutación [54]. Por lo tanto, el aumento de la frecuencia de conmutación no sólo degrada la eficiencia del sistema, sino que también la dinámica transitoria del convertidor [54].

Figura 8: Convertidor CA-CD reductor-elevador de dos etapas.

#### Convertidor SEPIC

El convertidor SEPIC, cuyo nombre viene del acrónimo en inglés de convertidor de inductor primario de un solo extremo o (Single-ended primary-inductor converter). Es una de las topologías que tiene la capacidad de reducir o aumentar el voltaje de salida [60], [61]. Este convertidor es empleado en aplicaciones de PFC, debido a que al operar en MCD la corriente de entrada del convertidor sigue de forma natural al voltaje de entrada [62]. El uso de esta topología simplifica su implementación, ya que no requiere el uso de filtros adicionales, debido a que la corriente de entrada no presenta el tercer armónico [2], [63].

Sin embargo, el uso del convertidor SEPIC sólo se recomienda para aplicaciones de baja potencia, debido al alto estrés eléctrico que presenta e incluso mucho mayor a las que

Figura 9: Convertidor CA-CD SEPIC.

puede presentar el convertidor elevador, cuando opera a los mismos niveles de potencia [64].

En [65], [66] se han estudiado los convertidores SEPIC sin puente de diodo de diodos, con el fin de reducir las pérdidas de potencia originadas por el proceso de conmutación de los semiconductores. Sin embargo, se reporta que no existe una reducción en el estrés eléctrico en los dispositivos semiconductores, lo que hace que este convertidor se encuentre limitado solo para aplicaciones menores de 150 W [66]. Otro de los inconvenientes que tiene el convertidor SEPIC está relacionado con el rizo de corriente de carga, ya que al tener una corriente de salida discontinua el valor del rizo se incrementa [11].

#### Convertidor Cuk

El convertidor Cuk mostrado en la Figura 10 recibe el nombre por Slobodan Cuk y al igual que el convertidor SEPIC, esta topología puede elevar o reducir el voltaje de salida [60]. Esta topología se diseña con el fin que el inductor  $L_2$  opere en MCD, para tener un factor de potencia cercano a la unidad, mientras que el inductor  $L_1$  opera en MCC lo que permite reducir el rizo de corriente de entrada [67].

Figura 10: Convertidor CA-CD Cuk.

Dentro de los principales inconvenientes que tiene esta topología al operar en MCD, son un alto estrés eléctrico en los dispositivos semiconductores. Esto provoca un aumento en las pérdidas de conducción y por consecuencia una disminución en la potencia nominal y la vida útil del convertidor [68]. Al igual que el convertidor reductor-elevador, el convertidor Cuk presenta un voltaje de salida con polaridad invertida, por lo que el uso solo se recomienda en aplicaciones de baja potencia [60], [69].

### Convertidor Zeta

El convertidor Zeta es otro de los convertidores utilizados en aplicaciones de PFC, cuya estructura se muestra en la Figura 11. Esta topología a diferencia del convertidor buckboost y SEPIC no presenta una corriente de salida de forma pulsante, por lo que permite tener un rizado de voltaje de salida menor y, además de permitir capacitores con valores pequeños en el bus CD de salida [70]. Este convertidor al operar los inductores  $L_1$  y  $L_2$  en MCD permite mejorar el factor de potencia, debido a que tiene un comportamiento de seguidor de voltaje, por lo que su FP es muy cercano a la unidad [70].

Figura 11: Convertidor CA-CD Zeta.

A diferencia de los convertidores boost, buck-boost, Cuk y SEPIC, el convertidor Zeta no presenta un alto contenido armónico en la corriente de la red. En [71] se reporta que el convertidor Zeta presenta una THD de corriente de alrededor de 5 %. Dentro las aplicaciones que han utilizado el convertidor Zeta, se encuentran en sistemas de iluminación LED, sistemas de cómputo y variadores de velocidad de motores [70], [72], [73].

#### Convertidor Reductor

El convertidor reductor es una de las topologías que se han abordado en aplicaciones de PFC, debido a su alta eficiencia al operar en baja potencia [74]. La topología convencional del convertidor reductor no es muy utilizada, debido a que presenta una forma onda de corriente de entrada pulsante [75]. Por lo que, requiere que se realicen diferentes modificaciones a su estructura para tener una corriente de entrada de forma continua [76].

Figura 12: Convertidor CA-CD Reductor.

En [77], [79] se reporta una modificación al convertidor reductor, la cual consiste en añadir un filtro LC después de la etapa rectificación, como se muestra en la Figura 12. Este

filtro está diseñado con el fin de hacer que la corriente de entrada sea continua y mitigar las componentes armónicas inyectadas hacia la red que son producidas por la conmutación del convertidor.

En [77] se propone que ambos inductores que conforman al convertidor mostrado en la Figura 12, operen en MCD para que tenga una corrección del factor de potencia de forma inherente. Sin embargo, al operar los inductores en MCD se tiene la desventaja de que los dispositivos semiconductores tienen un alto estrés eléctrico, debido a los picos de corriente existentes en el convertidor lo que impacta en la eficiencia [78]. Uno de los principales inconvenientes que tiene el convertidor está relacionada con el contenido armónico en la corriente de la red [80]. Esto se debe, a que la corriente de entrada presenta un ángulo de no conducción, lo que deteriora el factor de potencia [80], [82]. Se han reportado diferentes trabajos, donde abordan este problema como se reporta en [79], [81]. Las soluciones presentadas consisten en agregar un mayor número de elementos, lo que implica una reducción de la eficiencia y un aumento en la complejidad de control.

# 3.3.3. Análisis comparativo de convertidores CA-CD operados en Modo de Conducción Discontinua

En esta subsección se presenta un análisis comparativo entre las diferentes topologías de convertidores CA-CD anteriormente presentadas. El análisis se realizó con el fin de determinar los niveles de factor de potencia y THD de corriente de red, que presenta cada convertidor al operar en MCD. Los convertidores se diseñaron para que operaran bajo a las mismas condiciones nominales de potencia y voltaje de salida.

En la Tabla 1, se muestran los valores de los elementos que fueron utilizados para realizar simulación. Para todos los convertidores excepto para el convertidor reductor, se consideró un voltaje de entrada puramente sinusoidal de 35  $V_{rms}$  con una frecuencia de 60 Hz. La frecuencia de conmutación se estableció en 20 kHz.

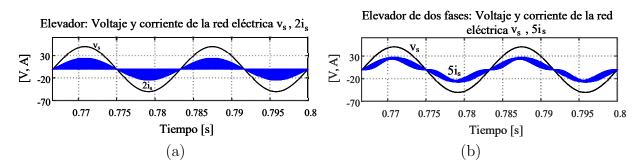

En la Figura 13, se muestran las formas de onda de voltaje y corriente de red de los convertidores elevador y elevador de dos fases. En los dos casos, la corriente y voltaje de entrada se encuentran en fase. Sin embargo, la forma de onda de corriente del convertidor elevador es discontinua y presenta una envolvente con la forma de onda de voltaje.

| Elevador  | Elevador de<br>dos fases | Reductor elevador | Reductor SEPIC elevador |     | Reductor<br>LC |

|-----------|--------------------------|-------------------|-------------------------|-----|----------------|

| $75\mu H$ | $200\mu H$               | 3mH               | $700\mu H$              | 1mH | $178\mu H$     |

| Elemento       | Elemento Elevador de |              | Reductor     | SEPIC        | Cuk          | Reductor      |

|----------------|----------------------|--------------|--------------|--------------|--------------|---------------|

|                |                      | dos fases    | elevador     |              |              | LC            |

| $L_1$          | $75\mu H$            | $200\mu H$   | 3mH          | $700\mu H$   | 1mH          | $178\mu H$    |

| $L_2$          |                      | $200\mu H$   | $40\mu H$    | $40\mu H$    | $100\mu H$   | $179\mu H$    |

| $C_1$          | $200\mu F$           | $200\mu F$   | $1\mu F$     | $3.35\mu F$  | $1.67\mu F$  | $0.47\mu F$   |

| $C_2$          |                      | _            | $200\mu F$   | $440\mu F$   | $470\mu F$   | $1000\mu F$   |

| d              | 37%                  | 44%          | 50%          | 33%          | 47%          | 29%           |

| R              | $100\Omega$          | $100\Omega$  | $100\Omega$  | $100\Omega$  | $100\Omega$  | $100\Omega$   |

| $F_{sw}$       | 20kHz                | 20kHz        | 20kHz        | 20kHz        | 20kHz        | 20kHz         |

| $V_{out}$      | 100 V                | 100 V        | 100 V        | 100 V        | 100 V        | 100 V         |

| $\overline{P}$ | 100 W                | 100 W        | 100 W        | 100 W        | 100 W        | 100 W         |

| $V_s$          | $35 V_{rms}$         | $35 V_{rms}$ | $35 V_{rms}$ | $35 V_{rms}$ | $35 V_{rms}$ | $127 V_{rms}$ |

Tabla 1: Parámetros de los convertidores

Los resultados numéricos indican que el convertidor elevador presenta un factor de potencia de 0.7 mientras que el convertidor elevador de dos fases es de 0.98. El índice de distorsión armónica de corriente de red para la topología elevadora es de 101 %, mientras para el elevador de dos fases es de 18.68 %.

Figura 13: Voltaje y corriente de red (a) del convertidor elevador y (b) elevador de dos fases.

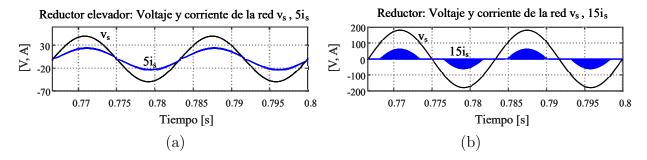

En la Figura 14, se muestran las formas de onda de voltaje y corriente de red correspondientes a los convertidores reductor-elevador y reductor. Las formas de onda de voltaje y corriente se encuentran en fase. En el caso de la forma de onda de corriente de red que presenta el convertidor reductor, tiene un ángulo de no conducción alrededor del cruce por cero.

Figura 14: Voltaje y corriente de red (a) del convertidor reductor-elevador y (b) reductor.

El factor de potencia que presentó el convertidor reductor-elevador fue de 0.96 y un THD de corriente de 3.31 %. El THD de corriente del convertidor reductor es mayor al que presentó al convertidor reductor, teniendo un nivel de 121 %, y un factor de potencia de 0.63.

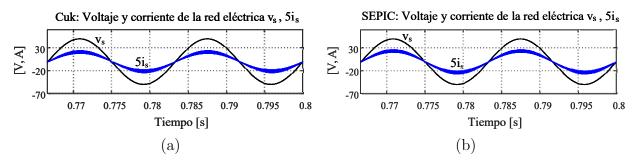

En la Figura 15, se muestran las formas de onda de voltaje y corriente de red, de los convertidores SEPIC y Cuk. Al igual que en el caso de los convertidores anteriores, las formas de onda de voltaje y corriente de la red se encuentran en fase. El valor de factor de potencia que presentan el convertidor Cuk y SEPIC es de 0.99. Los niveles de distorsión armónica de corriente de red para el convertidor Cuk y SEPIC son de 8.73 % y 5.58 % respectivamente.

Figura 15: Voltaje y corriente de red (a) del convertidor Cuk y (b) SEPIC.

En la Tabla 2, se muestra una comparativa entre las diferentes topologías en términos de sus parámetros de la calidad de la energía. Los convertidores SEPIC y Cuk son los que presentan factores de potencia mayores o iguales a 0.99. Sin embargo, el convertidor SEPIC es el que tiene un THD de corriente de entrada menor en comparación al convertidor Cuk.

Tabla 2: Parámetros de rendimiento de los convertidores.

| Elemento         | Elevador | Elevador de dos fases | Reductor elevador | SEPIC | Cuk   | Reductor<br>LC |

|------------------|----------|-----------------------|-------------------|-------|-------|----------------|

| FP               | 0.7      | 0.98                  | 0.96              | 0.99  | 0.99  | 0.63           |

| THD de corriente | 101 %    | 18.68%                | 3.31%             | 5.58% | 8.73% | 121 %          |

Por otra parte, el convertidor elevador de dos fases, es el que tiene un menor THD y rizo de corriente. Los convertidores que tiene un menor nivel de distorsión armónica de corriente, es el convertidor SEPIC y reductor-elevador.

4. Capítulo III: Marco teórico

# 4.1. Calidad de la energía

La eficiencia energética se ha vuelto cada vez más importante en los últimos años, especialmente para las empresas de suministro de energía y las industrias fabricantes de electrodomésticos, ya que tener sistemas eléctricos o electrónicos con una alta eficiencia implica un mejor aprovechamiento de la energía.

El término de la calidad de la energía se puede definir como la combinación entre la calidad de voltaje y la calidad de la corriente. Esto se puede determinar por aspectos relacionados con las desviaciones de voltaje o corriente en comparación a sus formas ideales. Una buena calidad de energía se alcanza cuando los voltajes y las corrientes en un sistema eléctrico son sinusoides puras y sus formas de onda no tienen desplazamiento ni distorsión armónica [77], [21]. Para que los equipos electrónicos aprovechen mejor la energía, deben tener una buena calidad de energía, es decir, un THD de corriente de red bajo y un factor de potencia cercano a la unidad.

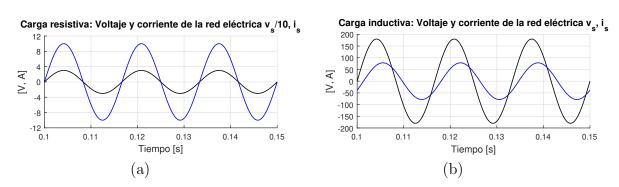

La mayoría de los dispositivos electrónicos utilizados en aplicaciones industriales y domésticas degradan la calidad energética de la red debido al uso de elementos reactivos y semiconductores. En la Figura 16 y Figura 17, se muestran las formas de onda de voltaje y corriente para tres ejemplos de cargas eléctricas comunes que se encuentran en aplicaciones industriales. La Figura 16 (a), corresponde a una carga puramente resistiva. En la cual, se observa que la forma de voltaje y corriente se encuentran en fase presentando un nulo contenido armónico en la corriente de red.

Figura 16: Formas de onda de voltaje y corriente de red (a) con carga puramente resistiva, (b) con carga puramente inductiva.

La Figura 16 (b) corresponde a las formas de onda de una carga puramente inductiva. En esta Figura se observa que la forma de onda de corriente se encuentra desfasada con respecto a la forma de voltaje. En este caso aunque el contenido armónico es nulo se presenta un factor de potencia menor a la unidad que existe un desfase entre la señal de voltaje y la señal de corriente de la red eléctrica.

La Figura 17 corresponde a las formas de voltaje y corriente de un rectificador basado en diodos de onda completa. Este tipo de sistemas es ampliamente utilizado en sistemas industriales como en electrodomésticos. La calidad de energía que presenta este sistema es baja, debido a que la forma de onda de corriente tiene un alto contenido armónico, por lo que el factor de potencia es bajo.

Figura 17: Formas de onda de voltaje y corriente de un rectificador de onda completa.

La presencia de armónicos en la corriente de CA puede ser perjudicial para algunos elementos. Por ejemplo los transformadores, debido que la presencia de armónicos en la corriente de red de CA, puede generar sobrecalentamiento, lo que causa una degradación en la vida útil del dispositivo.

Los niveles de contenido armónico que presenta una señal de voltaje o corriente puede ser cuantificado mediante el cálculo del THD (2) [87].

$$THD = \frac{\sqrt{\sum_{n=2}^{\infty} I_{n,RMS}^2}}{I_{1RMS}} \tag{2}$$

Donde  $I_{1,RMS}$  es el valor RMS de la componente fundamental de corriente y  $I_{n,RMS}$  representa el valor RMS de la n-enésima componente armónica.

## 4.2. Normativas relacionadas con la calidad de la energía

Los niveles de armónicos permitidos en sistemas de baja y alta potencia están establecidos por normas que son emitidas principalmente por el Instituto de Ingenieros Eléctricos y Electrónicos (IEEE, Institute of Electrical and Electronics Engineers) y por la Comisión Electrotécnica Internacional (IEC, International Electrotechnical Commission).

La norma IEEE-519, establece el porcentaje de contaminación armónica que un sistema eléctrico puede inyectar a la red eléctrica. Este porcentaje de THD permitido, es determinado mediante la relación que existe entre la corriente máxima de corto circuito

en un punto de conexión común (PCC)  $I_{sc,RMS}$  y las corrientes de carga  $I_{1,RMS}$ , como se expresa en (3). La Tabla 3, Tabla 4 y Tabla 5 describen el porcentaje permitido de los armónicos impares en la corriente de acuerdo coeficiente de relación para tres diferentes niveles de potencia.

$$\frac{I_{sc,RMS}}{I_{1,RMS}} \tag{3}$$

Tabla 3: Límite de distorsión de corriente para sistemas de distribución general de  $120~\rm V$  a  $69~\rm kV$  [88]

| $\frac{I_{sc,RMS}}{I_{1,RMS}}$ | h < 11 | $11 \le h < 17$ | $17 \le 23$ | $23 \le h < 35$ | $35 \le h$ | THD  |

|--------------------------------|--------|-----------------|-------------|-----------------|------------|------|

| < 20                           | 4      | 2.0             | 1.5         | 0.6             | 0.3        | 5.0  |

| 20-50                          | 7.0    | 3.5             | 2.5         | 1.0             | 0.5        | 8.0  |

| 50-100                         | 10.0   | 4.5             | 4.0         | 1.5             | 0.7        | 12.0 |

| 100-1000                       | 12.0   | 5.5             | 5.0         | 2.0             | 1.0        | 15.0 |

| > 1000                         | 15.0   | 7.0             | 6.0         | 2.5             | 1.4        | 20.0 |

Tabla 4: Límite de distorsión de corriente para sistemas de distribución general de 69.001 kV a 161 kV [88]

| $\frac{I_{sc,RMS}}{I_{1,RMS}}$ | h < 11 | $11 \le h < 17$ | $17 \le 23$ | $23 \le h < 35$ | $35 \le h$ | THD  |

|--------------------------------|--------|-----------------|-------------|-----------------|------------|------|

| < 20                           | 2.0    | 3.5             | 0.75        | 0.3             | 0.15       | 2.5  |

| 20-50                          | 3.5    | 2.75            | 1.5         | 0.5             | 0.25       | 4.0  |

| 50-100                         | 5.0    | 2.25            | 2.0         | 0.75            | 0.35       | 6.0  |

| 100-1000                       | 6.0    | 2.75            | 2.5         | 1.0             | 0.5        | 7.5  |

| > 1000                         | 7.5    | 3.5             | 3.0         | 1.25            | 0.7        | 10.0 |

Tabla 5: Límite de distorsión de corriente para sistemas de transmisión general de >161 kV [88]

| $\frac{I_{sc,RMS}}{I_{1,RMS}}$ | h < 11 | $11 \le h < 17$ | $17 \le 23$ | $23 \le h < 35$ | $35 \le h$ | THD  |

|--------------------------------|--------|-----------------|-------------|-----------------|------------|------|

| < 50                           | 2.0    | 1.0             | 0.75        | 0.3             | 0.15       | 2.5  |

| $\geq 50$                      | 3.0    | 1.5             | 1.15        | 0.45            | 0.22       | 3.75 |

La norma IEC 61000 y EN 61000 establecen límites de armónicos permitidos en sistemas de baja frecuencia en redes industriales y domésticas. La IEC establece en su estándar IEC 61000-3-2 que los fabricantes de dispositivos eléctricos y electrónicos limiten el consumo de armónicos de corriente de sus productos. Los equipos eléctricos y electrónicos pueden clasificarse en cuatro tipos según los criterios evaluados por los miembros de la IEC, los cuales se enlistan en la Tabla 6.

Tabla 6: Clasificación de equipos eléctricos y electrónicos de acuerdo a la norma IEC61000 [89]

| Clasificación A                              | Clasificación B                                                                                                                                   |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Equipos trifásicos equilibrados, equipos mo- | Herramientas de potencia portátiles                                                                                                               |

| nofásicos no incluidos en otras clases.      |                                                                                                                                                   |

| Clasificación C                              | Clasificación D                                                                                                                                   |

| Equipos de iluminación de más de 25 W.       | Computadoras personales y monitores de computadoras personales. Nota: El equipo debe tener un nivel potencia de 75 W hasta y no superior a 600 W. |

De acuerdo a la norma IEC 61000 se establece que existen tres principales fuentes de armónicos, entre las cuales se encuentran equipos de sistemas de energía, cargas industria-les y cargas residenciales. Los límites permitidos de armónicos establecido por la norma IEC 61000 se muestran en la Tabla 7.

Tabla 7: Niveles de armónicos para equipos de los diferentes grupos [89]

|               |             | 1 1         | . 1           | 0 1 [ ] |

|---------------|-------------|-------------|---------------|---------|

| Armónicos [A] | Clase A [A] | Clase B [A] | Clase C [% de | Clase D |

|               |             |             | fund]         | [mA/W]  |

| 3             | 2.3         | 3.45        | 30x           | 3.4     |

| 5             | 1.14        | 1.71        | 10            | 1.9     |

| 7             | 0.77        | 1.15        | 7             | 1.0     |

| 9             | 0.4         | 0.6         | 5             | 0.5     |

| 11            | 0.33        | 0.49        | 3             | 0.35    |

| 13            | 0.21        | 0.315       | 3             | 3.85/13 |

#### Factor de Potencia

Otro de los aspectos importantes relacionados con la calidad de la energía es el factor de potencia. El cual se define como la relación que existe entre la potencia activa y la potencia aparente y que describe la relación entre la potencia de trabajo y la potencia total consumida, como se muestra en (4) [87].

$$FP = \frac{P}{S} \tag{4}$$

Donde P es la potencia activa y S es la potencia aparente. El factor de potencia es un indicador del correcto aprovechamiento de la energía. Por lo que, un bajo factor de potencia implica un mal aprovechamiento de la energía. El consumo de excesivo de corriente reactiva en instalaciones eléctricas pueden ser una causante de un bajo factor de potencia. Las cargas inductivas como motores, transformadores, balastros, entre otras, son las principales cargas que originan un desfase entre la señal de voltaje y corriente.

Dentro de las implicaciones de tener un bajo FP, se encuentra una penalización por parte de la empresa encargada del suministro eléctrico. Además, de presentar un aumento en las pérdidas en los conductores eléctricos y en el consumo de la tarifas eléctricas, lo que implica pérdidas económicas para los usuarios.

Una de las soluciones utilizadas en la industria para aumentar el factor de potencia, es mediante un banco de capacitores, que permite compensar el consumo de corriente reactiva. Existen tres tipos de compensación mediante banco de capacitores, la cual se en lista a continuación.

## Compensación individual

La compensación individual consiste en colocar un capacitor en paralelo junto al equipo eléctrico, de manera que la potencia reactiva fluye solamente sobre los conductores entre el equipo eléctrico y el capacitor.

## Compensación grupal

La compensación grupal consiste en realizar la compensación de varios equipos a las vez mediante un banco de capacitores que comparten en común. Este tipo de compensación, es utilizada en sistema de iluminación de tipo fluorescentes.

## Compensación central

Esta compensación central consiste en colocar el banco de capacitores cerca de los tableros de distribución. Dentro de las ventajas que tiene este tipo de compensación se encuentra una mejor utilización de la capacidad del banco de capacitores y una fácil supervisión.

5. Capítulo IV: Sistemas de rectificación con una etapa de convertidor CD-CD.

## 5.1. Introducción

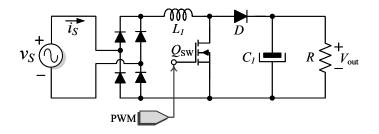

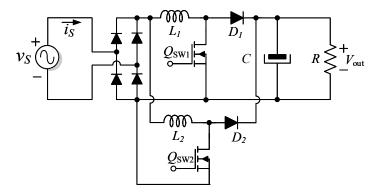

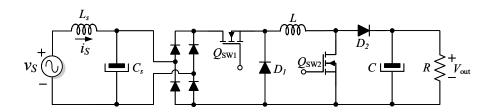

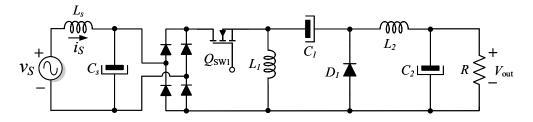

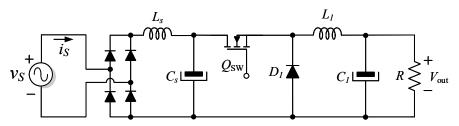

En este capítulo se presenta el estudio de dos topologías de convertidores CA-CD, las cuales se plantean ser utilizadas en aplicaciones de corrección de factor de potencia. Los convertidores propuestos se basan en el esquema mostrado en la Figura 18, y consisten en utilizar dos etapas de conversión de energía, una de corriente alterna a corriente directa y la segunda de corriente directa a corriente directa.

Figura 18: Esquema de los convertidores propuesto.

La etapa de conversión de CA-CD esta es conformada por un rectificador de onda completa no controlado, sin capacitor de alisamiento. El propósito de esta etapa, es convertir la energía de CA proveniente de la red eléctrica a una forma de CD.

La etapa correspondiente al convertidor CD-CD, tiene el propósito de mantener el voltaje de salida del sistema regulado. Esta etapa de conversión de energía se basa en el principio de funcionamiento de un convertidor reductor convencional para los dos casos de los convertidores propuestos.

En los dos convertidores propuestos se tiene un inductor  $L_s$  entre la etapa de rectificación y del convertidor CD-CD. La incorporación de este filtro tiene el propósito de que actué como un filtro de corriente, además, de hacer que la corriente de CA sea continua.

Los convertidores CD-CD se diseñan para que operen en MCD, debido que se ha demostrado que al operar en MCD el convertidor reductor tiene buenas propiedades para ser empleado en aplicaciones de PFC [77]. El inductor  $L_s$  está diseñado para operar en MCC, para reducir el rizo de corriente de lado de la red eléctrica.

Se propone validar los convertidores tanto en lazo abierto como en lazo cerrado. Para el caso de la validación en lazo cerrado se propone una ley de control con dos objetivos de control, los cuales consisten en un lazo de regulación de voltaje y seguimiento de corriente.

# 5.2. Convertidores reductores con mejora en el factor de potencia

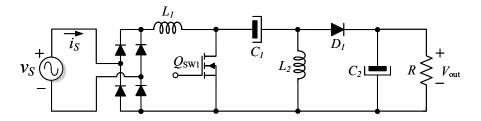

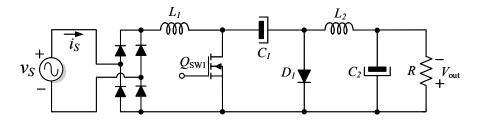

En la Figura 19, se muestra uno de los dos convertidores propuestos en este trabajo de tesis. El convertidor propuesto se basa en un convertidor de tipo reductor, el cual presenta las características ya mencionadas en la sección anterior.

Figura 19: Convertidor reductor multifase propuesto.

El convertidor está conformado por un puente de diodos no controlado, seguido de un filtro LC y un convertidor CD-CD de tipo reductor. Para este caso el convertidor reductor tiene cuatro celdas de conmutación conectadas en paralelo, las cuales están conformadas por un MOSFET, diodo e inductor. La incorporación de estas celdas de conmutación se realiza con el fin de reducir el estrés eléctrico en los elementos semiconductores.

#### 5.2.1. Análisis del convertidor reductor en MCD

Para la obtención de los parámetros de operación del convertidor reductor multifase en estado estable, se proponen varias consideraciones. Una de ellas es asumir que el voltaje a través del capacitor  $C_s$  se mantiene constante durante un periodo de conmutación. Por lo que, se puede sustituir por una fuente de voltaje CD. Se analiza primeramente una única celda de conmutación.

Para determinar las ecuaciones que describen el convertidor propuesto se pueden encontrar a partir del análisis de un convertidor reductor convencional operado en MCD. En la Figura 20, se muestra los circuitos equivalentes del convertidor. El convertidor reductor presenta tres modos de operación que están determinados por el modo de operación del inductor  $L_1$ .

Figura 20: Modos de operación del convertidor (a) Modo 1, (b) Modo 2 y (c) Modo 3.

En la Figura 20 (a) se muestra el circuito equivalente para el Modo 1. En este modo, el interruptor  $Q_{sw1}$  se encuentra conduciendo (ON) como se muestra en la Figura 21 (a). Por lo que, la corriente que pasa a través del inductor  $L_1$  crece de forma lineal desde cero a un valor máximo, como se observa en la Figura 21 (b). En la Figura 21 (c), se muestra el voltaje entre las terminales entre drain-source que presenta el MOSFET.

Figura 21: Formas de onda del convertidor (a) Ciclo de trabajo, (b) corriente del inductor  $L_1$  y (c) voltaje drenaje-fuente.

Analizando el circuito equivalente para el Modo 1, mostrado en la Figura 20 (a) se tiene que

$$V_L + V_C - V_{in} = 0 ag{5}$$

donde el voltaje del inductor puede ser expresado como en (6).

$$V_L = L_1 \, \frac{\Delta I}{\Delta t} = L \, \frac{I_2 - I_1}{dT_s - 0} \tag{6}$$

Donde  $I_2$  es el máximo valor de la corriente del inductor  $L_s$ , e  $I_1$  el mínimo y  $dT_s$  es el tiempo que dura activo el Modo 1. Al sustituir (6) en (5) se tiene que

$$L_1 \frac{I_2 - I_1}{dT_s} = V_{in} - V_{out} \tag{7}$$

Tomando en cuenta que  $I_1=0A$  debido a que el inductor opera en MCD y que  $I_2$  se puede definir como  $I_{max}$ , (7) se puede expresar como en (8).

$$L_1 \frac{I_{max}}{dT_s} = V_{in} - V_{out} \tag{8}$$